## **TOSHIBA**

### TECHNICAL TRAINING MANUAL

# 3 LCD DATA PROJECTOR TLP411U TLP411E

## **CONTENTS**

| SECTION I<br>MAIN POWER SUPPLY                           | 2-3. Level Shifter Circuit (Q965 – Q968, R1044) 4-4 |

|----------------------------------------------------------|-----------------------------------------------------|

|                                                          | 2-4. Black Limiter (Q969, Q970) 4-4                 |

| CIRCUIT 1-1                                              | 2-5. Inverted Signal Amplifiers (Q974 – Q981) 4-4   |

| 1. OUTLINE1-2                                            | (Q9/4 – Q981) 4-4<br>2-6. Switch Circuit            |

| 1-1. Block Diagram 1-2                                   | (Q982 µPD74HC4066A)4-4                              |

| 2. DESCRIPTION ABOUT                                     | 2-7. Sample & Hold Circuit 4-5                      |

| CIRCUIT OPERATION1-2                                     | 2-8. LCD Panel 4-7                                  |

| 2-1. Surge Absorber Circuit 1-2                          |                                                     |

| 2-2. Noise Filter Circuit                                |                                                     |

| 2-3. Rush Current Protection Circuit 1-3                 | SECTION V                                           |

| 2-4. Smoothing/Rectifying Circuit 1-3                    |                                                     |

| 2-5. Inverter Circuit (Flyback) 1-4                      | <b>MICROCOMPUTER 5-1</b>                            |

| 2-6. Primary Control Circuit 1-4                         | 1. SYSTEM OUTLINE5-2                                |

| 2-7. Secondary Rectification &                           |                                                     |

| Smoothing Circuit 1-5                                    | 2. SYSTEM MICROCOMPUTER5-4                          |

| 2-8. +6V Detection Circuit                               | 3. POWER SUPPLY RESET                               |

| 2-9. +6V, +S6V, +15.5V Overvoltage<br>Protection Circuit | PROCESS5-5                                          |

| 2-10. +6V, +S6V Over Current                             | 4. NON-VOLATILE MEMORY                              |

| Protection Circuit 1-6                                   | PROCESS5-5                                          |

| 2-11. Output ON/OFF Circuit 1-6                          |                                                     |

| 2-12. ON/OFF Control Circuit 1-6                         | 5. REMOTE CONTROL                                   |

|                                                          | RECEPTION PROCESS5-6                                |

|                                                          | 6. RS-232C TRANSMIT/                                |

| SECTION II                                               | RECEIVE PROCESS5-6                                  |

| LAMP HIGH VOLTAGE                                        | 7. STATUS READ PROCESS5-7                           |

| POWER SUPPLY                                             | 8. STATUS DISPLAY PROCESS5-7                        |

| CIRCUIT 2-1                                              |                                                     |

| CIRCUIT 2-1                                              | 9. ON-SCREEN DISPLAY                                |

| 1. LAMP HIGH VOLTAGE                                     | PROCESS5-8                                          |

| <b>POWER SUPPLY2-2</b>                                   | 10. VIDEO MODE FETCH                                |

|                                                          | PROCESS5-8                                          |

|                                                          | 11. VIDEO SYSTEM CONTROL                            |

| SECTION III                                              | PROCESS5-9                                          |

| <b>OPTICAL SYSTEM 3-1</b>                                |                                                     |

|                                                          | 12. PANEL SYSTEM CONTROL                            |

| 1. CONFIGURATION3-2                                      | PROCESS5-10                                         |

|                                                          | 13. VARIOUS DISPLAY                                 |

|                                                          | MODES5-11                                           |

| SECTION IV                                               | 14. APPLICABLE SIGNAL5-12                           |

| RGB DRIVE CIRCUIT 4-1                                    |                                                     |

|                                                          | 15. RS-232C CONTROL                                 |

| 1. OUTLINE4-2                                            | METHOD5-13                                          |

| 2. CIRCUIT DESCRIPTION4-2                                | 16. RS-232C COMMAND LIST5-13                        |

| 2-1. Level Shifter (Q945 – Q953) 4-2                     | -                                                   |

| 2-2. Gamma (g) Circuit 4-3                               |                                                     |

| SECTION VI                                    | SECTION VIII                          |

|-----------------------------------------------|---------------------------------------|

| DIGITAL CIRCUIT 6-1                           | CCD CAMERA CIRCUIT 8-1                |

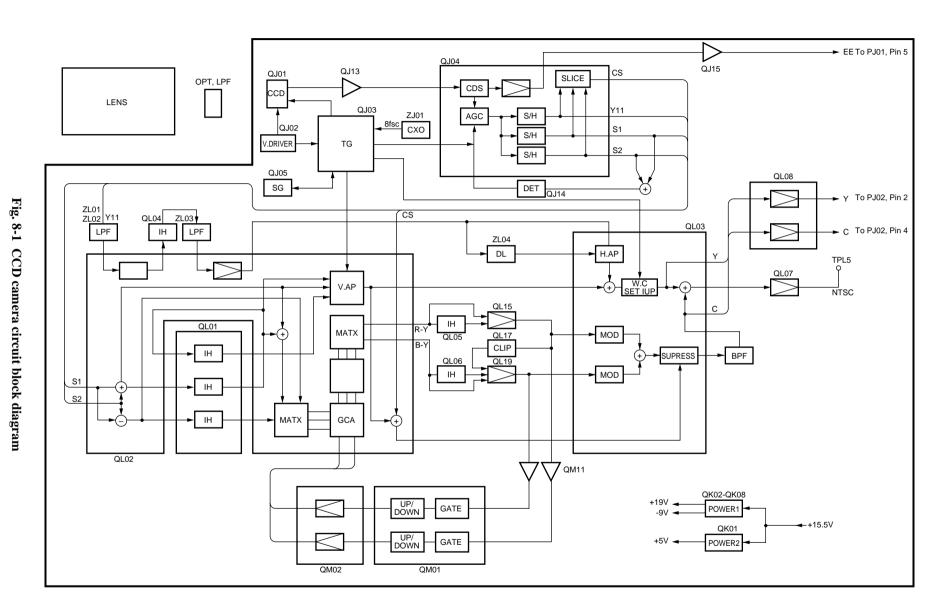

| 1. DIGITAL CIRCUIT                            | 1. OUTLINE8-2                         |

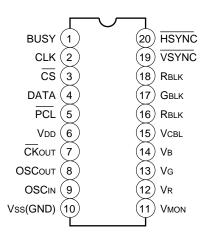

| <b>OPERATION6-2</b>                           | 1-1. CCD and Drive/Sync Signal        |

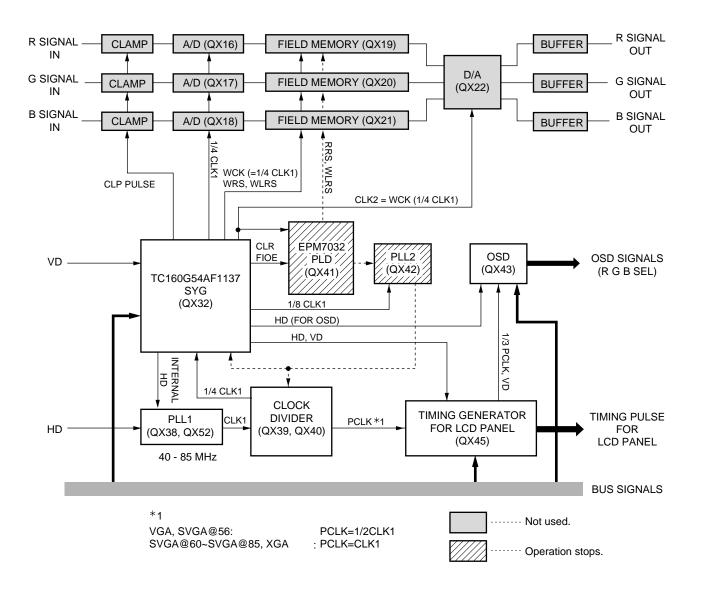

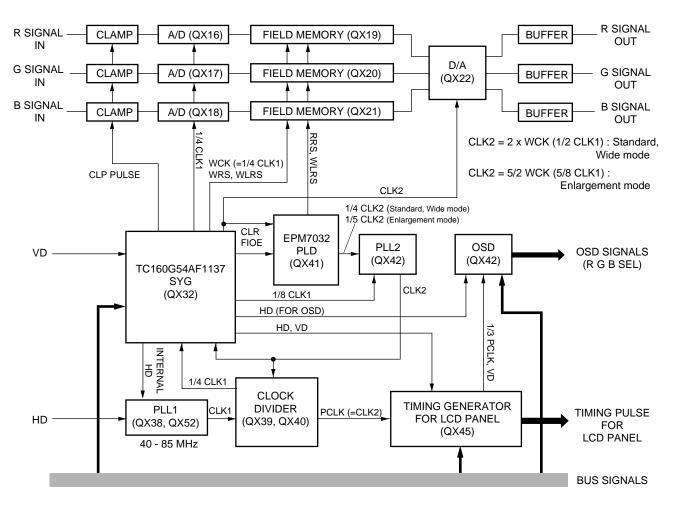

| 1-1. Display Mode 6-2                         | Generation Circuit (SG) 8-2           |

| 1-2. RGB Signal Input                         | 1-2. Pre-amp Circuit (CDS) 8-2        |

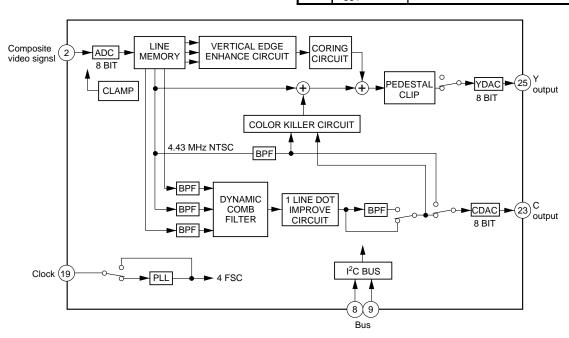

| 1-3. NTSC Signal Input 6-4                    | 1-3. Video Signal Process Circuit     |

| 1-4. PAL/SECAM Signal Input 6-4               | (PRO, ENC, AWB) 8-2                   |

| 2 1                                           | 1-4. Power Supply Circuit 8-2         |

| 2. CIRCUIT DESCRIPTION6-5                     |                                       |

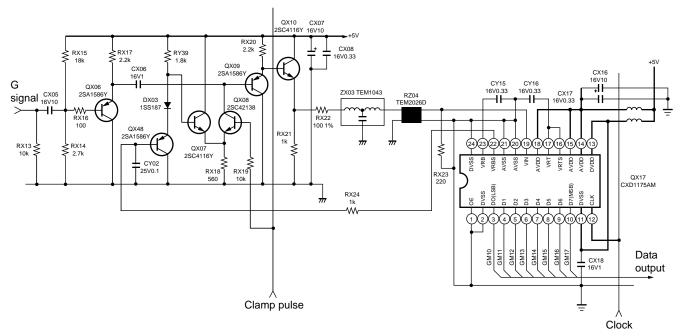

| 2-1. Clamp Circuit                            |                                       |

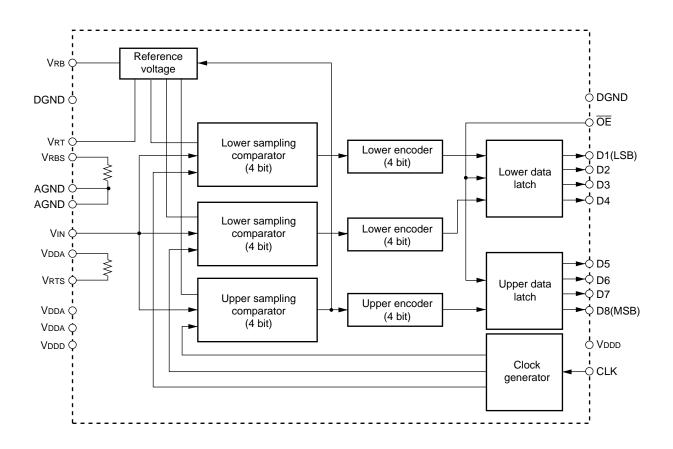

| 2-2. A/D Converter                            | SECTION IX                            |

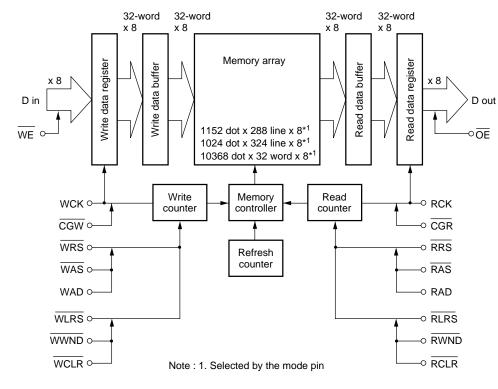

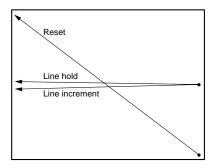

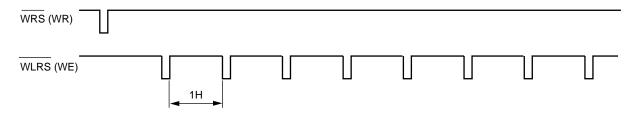

| 2-3. Memory                                   |                                       |

| 2-4. PLD Circuit                              | FLUORESCENT LAMP                      |

| 2-5. D/A Converter 6-11                       | INVERTER CIRCUIT 9-1                  |

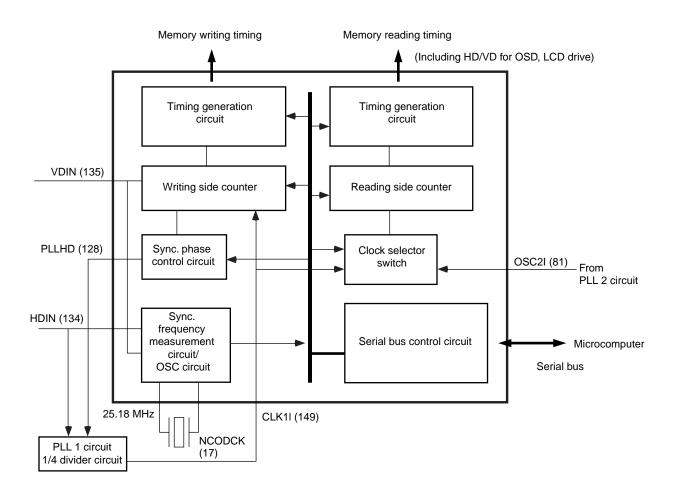

| 2-6. Memory Control and Sync Process IC 6-13  | 1. OPERATING DESCRIPTION9-2           |

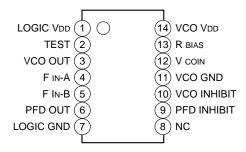

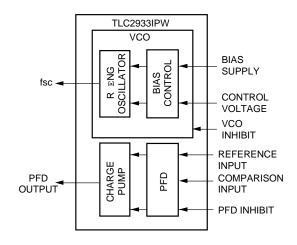

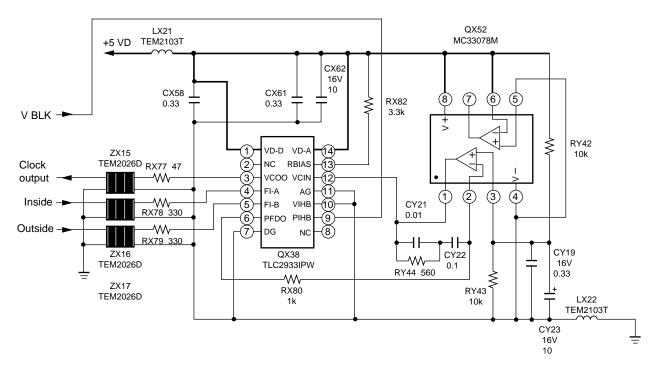

| 2-7. PLL Circuit (1)                          |                                       |

| 2-8. PLL Circuit (2)                          | 2. TROUBLESHOOTING9-3                 |

| 2-9. Liquid Crystal Panel Timing              | 2-1. Fluorescent does not turn on 9-3 |

| Generation Circuit 6-17                       | 3. CIRCUIT DIAGRAM9-4                 |

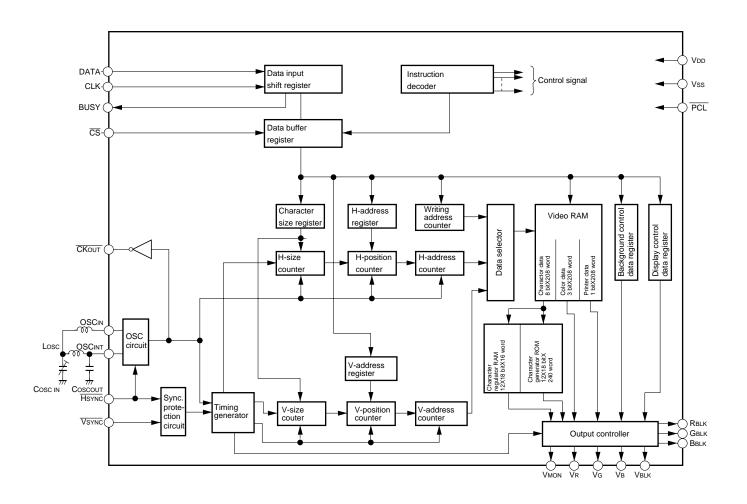

| 2-10. On-screen Character                     | J. CIRCUIT DITORINI                   |

| Generation Circuit 6-23                       |                                       |

|                                               |                                       |

| SECTION VII                                   |                                       |

| VIDEO SIGNAL PROCESS                          |                                       |

| CIRCUIT 7-1                                   |                                       |

| CIRCUIT /-1                                   |                                       |

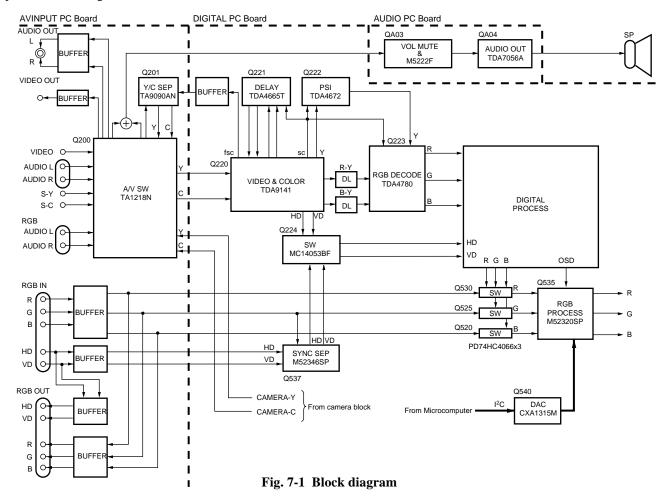

| 1. OUTLINE7-2                                 |                                       |

| 1-1. Circuit Configuration                    |                                       |

| 1-2. Video Signal Demodulation Block 7-2      |                                       |

| 1-3. RGB Signal Amplification                 |                                       |

| Circuit Block 7-2                             |                                       |

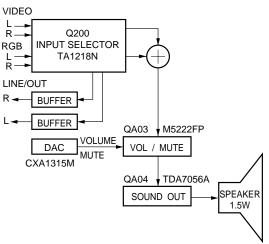

| 1-4. Audio Signal Amplification Block 7-2     |                                       |

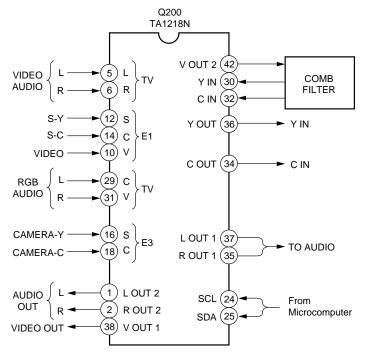

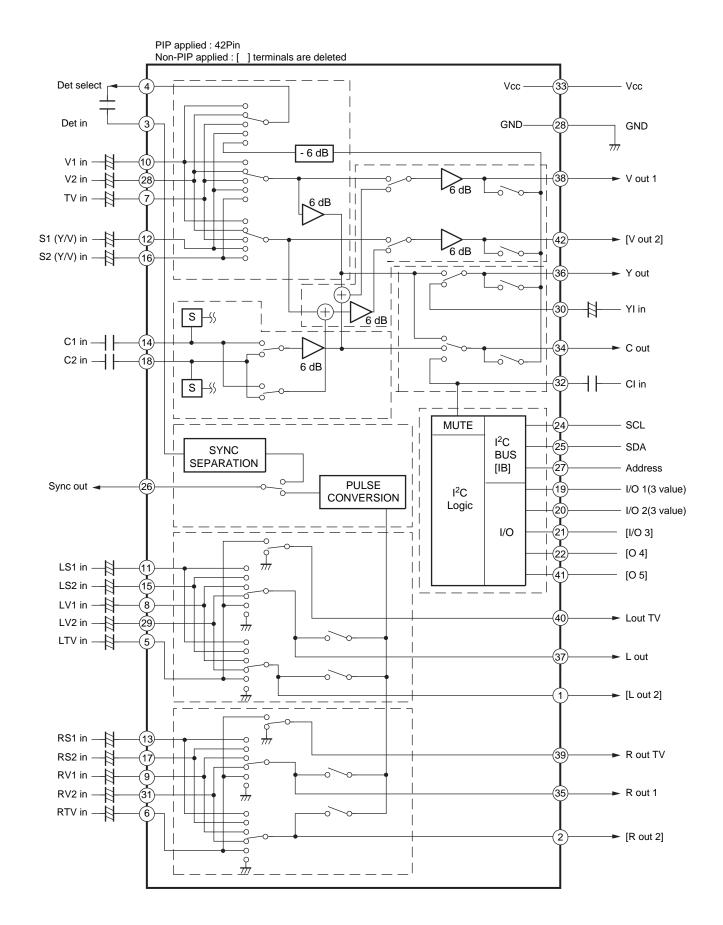

| 2. INPUT/OUTPUT SIGNAL                        |                                       |

| SWITCH CIRCUIT7-3                             |                                       |

| 2-1. Audio/Video Signal Switch Circuit 7-3    |                                       |

| 2-2. Input Signals                            |                                       |

|                                               |                                       |

| 3. VIDEO DEMODULATION                         |                                       |

| BLOCK7-5                                      |                                       |

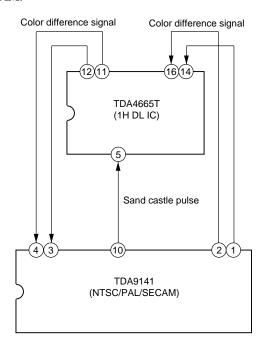

| 3-1. YC Separation Circuit                    |                                       |

| 3-2. Video/Color Circuit                      |                                       |

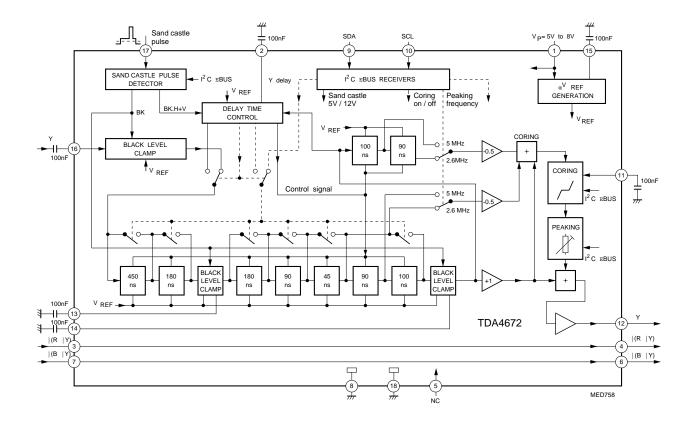

| 3-3. Luminance (Y) Signal Process Circuit 7-7 |                                       |

| 3-4. Color Signal Process Circuit             |                                       |

| 3-5. Picture Sharpness Correction Circuit 7-8 |                                       |

| 3-6. RGB Demodulation                         |                                       |

| 3-7. Audio Circuit 7-11                       |                                       |

| 4. RGB SIGNAL PROCESS                         |                                       |

| CIRCUIT7-11                                   |                                       |

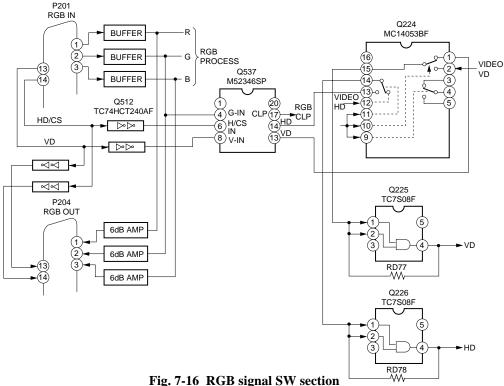

| 4-1. RGB Signal SW Section 7-11               |                                       |

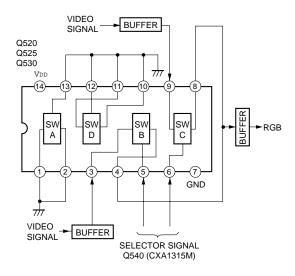

| 4-2. Video/RGB Signal SW Section 7-12         |                                       |

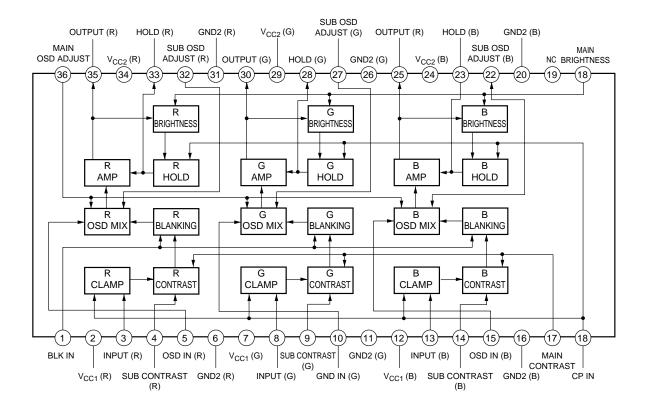

| 4-3. RGB Signal Amplifier Section 7-12        |                                       |

| 4-4. Microcomputer Interface 7-13             |                                       |

## SECTION I MAIN POWER SUPPLY CIRCUIT

#### 1. OUTLINE

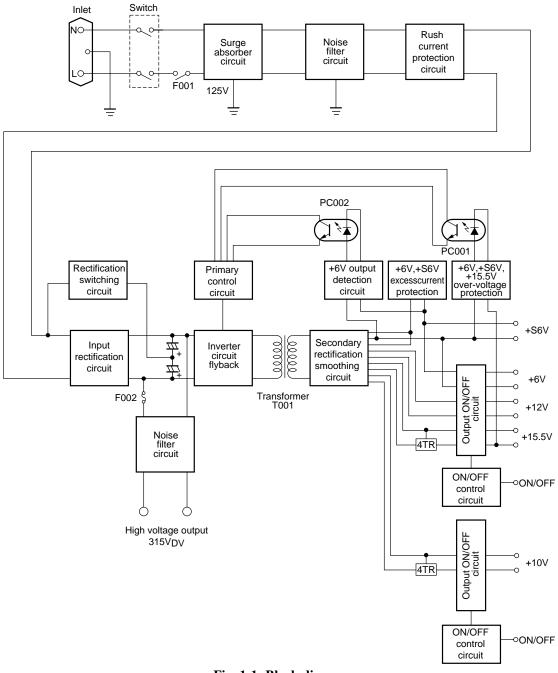

The power supply circuit operates on AC as input and outputs DC (+S6V, +6V, +10V, +12V, +15.5V) through inverter after rectification and smoothing of the AC power. ON/OFF function is provided for outputs other than +S6V by the external signal. It is also capable of providing high voltage output with inverter drive for halogen lamp. Fig. 1-1 shows the block diagram.

## 2. DESCRIPTION ABOUT CIRCUIT OPERATION

#### 2-1. Surge Absorber Circuit

The surge absorber circuit consists of protection element (varistor) and spark gap on the pattern surface on the PC board, making it possible to protect the power from being destroyed by lighting stroke and impulse invaded from external or from malfunction.

#### 1-1. Block Diagram

Fig. 1-1 Block diagram

#### 2-2. Noise Filter Circuit

The noise filter circuit only protects the noise generated by the power source from leaking out to AC line and from entering of the external noise inside the power. This circuit is effective for both normal and common noise.

#### 2-3. Rush Current Protection Circuit

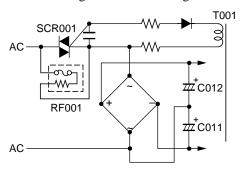

When AC power is, via D001, rectified and directly applied to C011 and C012, rush current runs through C011 and C012 as shown in Fig. 1-3. The current degrades the contact point of SW001. This rush current is controlled by the circuit shown in Fig. 1-2, preventing the degradation of the contact point.

Before the power activation, there exists no induced voltage in T001. SCR001 is in the OFF state. Rectified AC current runs through RF001 and charges C011 and C012.

Fig. 1-2

Rush current

Fig. 1-3

With this, RF001 becomes charging resistance and is suppressed less than 30A. Then, when the charging voltage of C011 and C012 becomes more than the activation voltage, the inverter starts oscillation (activation) and the voltage is generated in the T001. This voltage is used for trigger voltage for SCR001, turns on the SCR001 and short-circuits the RF001. As a result, the rectified current flows into C011 and C012, eliminating the power loss by RF001 in the normal operation state.

#### 2-4. Smoothing/Rectifying Circuit

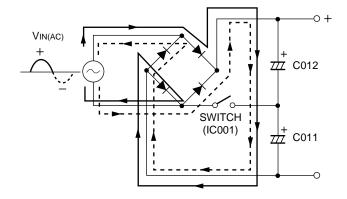

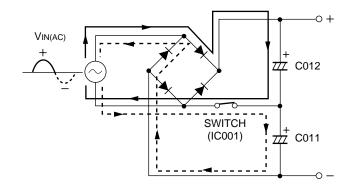

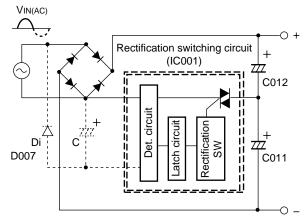

The input voltage of the unit is set to work in the range of AC100  $\sim$  120V and AC220  $\sim$  240V. To keep the AC rectification output voltage in almost the constant level, the voltage doubler rectification is employed for the AC100  $\sim$  120V input and the bridge rectification for the AC220  $\sim$  240V input. An exclusive IC is used to switch the voltage doubler rectification and the bridge rectification. Figs. 1-4, 1-5 and 1-6 show the basic circuits.

When the switch is turned off, each of a positive and negative half-wave voltage of  $V_{IN\ (AC)}$  is charged to C012 and C011, and the bridge rectification voltage is developed from the output terminal. On the other hand, when the switch is turned on, a positive half-wave voltage of  $V_{IN\ (AC)}$  is charged to C012 through the circuit shown by  $\longrightarrow$  and a negative half-wave voltage of  $V_{IN\ (AC)}$  is charged to C011 through the circuit shown by  $\longrightarrow$ . The voltage doubler of the half-wave rectification voltage is developed from the output terminal.

Fig. 1-4 Bridge rectification (SW: OFF)

Fig. 1-5 Voltage doubler rectification (SW: ON)

The half-wave rectification for  $V_{IN}$  (AC) is carried out by C and Di (D007) shown in the dotted line ----. When the input voltage is low, the triac is turned on (voltage doubler rectification) and when the input voltage high, the triac is turned off (bridge rectification).

Fig. 1-6

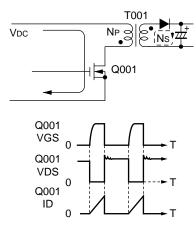

#### 2-5. Inverter Circuit (Flyback)

The current indicated with \_\_\_\_ to the converter transformer is turned on/off by the FET switch of Q001 operation. In the OFF state, the current indicated with \_\_\_\_ flows.

Signal is supplied to gate from the primary control circuit. With this, Q001 starts switching operation.

Gate voltage, drain voltage, and current waveform of Q001 are shown in Fig. 1-7.

Fig. 1-7

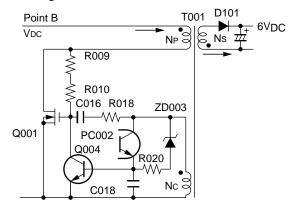

#### 2-6. Primary Control Circuit

The control system employs automatic flyback system by timing capacitor.

In the circuit diagram in Fig. 1-8, when power is turned on, input voltage  $V_{DC}$  is applied to B point. Voltage is applied to Q001 gate via R009 and R010. Then Q001 is activated. When Q001 is turned on, the drain current begins to flow as shown in Fig. 1-7 and input voltage is applied to NP winding.

Fig. 1-8

The voltage  $V_{NC} = N_C/N_P \times V_{DC}$  is generated in the  $N_C$  winding and voltage is supplied to Q001 gate through R018 and C016. At the same time, C018 is charged through ZD003 and R020.

When the electric potential of C018 rises up to  $V_{BE}$  (Sat) = approx. 0.7V, Q004 is turned on and Q001 is turned off.

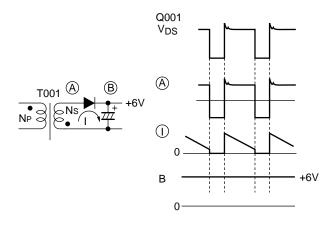

That is, ON period of Q001 is determined by the time constant of ZD003, R020 and C018. When Q001 becomes off, the energy (flyback) accumulated in the transformer T001 is output through D101. When this energy becomes zero, D101 becomes off. For there exists a slight residual energy in N<sub>S</sub> winding, by means of which voltage is generated in the gate winding N<sub>C</sub>, which turns on the Q001 again to resume switching operation.

On the other hand, when the voltage output through D001 is rectified by the secondary rectifying/smoothing circuit, when the voltage is detected by +6V detection circuit, PC002 becomes on. This shortens the time constant to charge C018. At the same time, the ON period of Q001 is controlled and the output voltage (+6V) becomes stable.

## 2-7. Secondary Rectification & Smoothing Circuit

High-voltage applied to  $N_P$  becomes, as mentioned previously, pulse by means of the switching operation and then converted to low voltage at both ends of the secondary side winding  $N_S$  via T001 and is output after rectification/smoothing.

Fig. 1-9

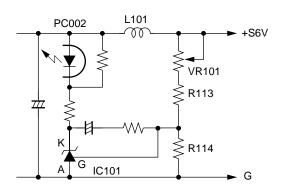

#### 2-8. +6V Detection Circuit

+6V voltage is divided by VR101, R113 and R114, it is input to the gate of IC101 and then it is compared with the reference voltage of that IC. This potential difference flows into PC002 as current variation which is then transferred to the primary side control circuit to control output voltage.

Fig. 1-10

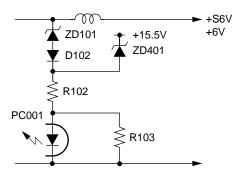

## 2-9. +6V, +S6V, +15.5V Overvoltage Protection Circuit

As shown in Fig. 1-9, the overvoltage of +6V and +S6V is detected by ZD101 and the overvoltage +15.5V is detected by ZD401.

When the overvoltage is detected, current flows to zener diode, the current then flows to PC001. This is transferred to the primary control circuit and trigger signal is given to the gate of thyristor SCR002 to short-circuit the gate of Q001. As a result, Q001 turns off and the oscillation stops.

The circuit is put to the latch mode. Therefore, no activation is possible even overvoltage state is released. Activation is made possible by reentry of input.

Fig. 1-11

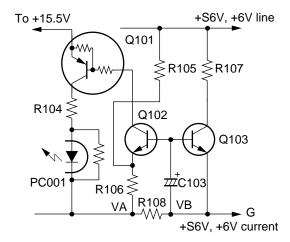

#### 2-10. +6V, +S6V Over Current Protection Circuit

As shown in Fig. 1-12, this circuit detects the over current by differential amplifier consisting of Q102 and Q103. The reference voltage is produced by voltage division of R105 and R106 using the +S6V as voltage source. This voltage called VA (+S6V x R106/R105 + R106) is compared with Voltage VB (Ioc x R108) generated by over current. Q101 and Q102 turn on under the VA < VB condition, by means of which the current is supplied to PC001. This is transferred to the primary control circuit. The rest of operation is the same as item 2-9.

Fig. 1-12

#### 2-11. Output ON/OFF Circuit

+15.5V and +10V outputs can be turned on/off by 4-terminal regulators IC401 and IC201. +5V and +6V outputs can be turned on/off by POWER MOSS FET (Q106, Q302). ON/OFF signal is given by the following ON/OFF control circuit.

#### 2-12. ON/OFF Control Circuit

This circuit controls the circuit of item 2-11, which delays the external signal by the integration circuits (R118 and C108) to send signals to each output circuit. Signal level is TTL level. Each output becomes off at "L" and becomes on at "H" approximately 300 ms later.

The ON/OFF signal of +12V is input from pin 2 of CN104 and turns Q302 ON/OFF passing through Q301 and PC101.

# SECTION II LAMP HIGH VOLTAGE POWER SUPPLY CIRCUIT

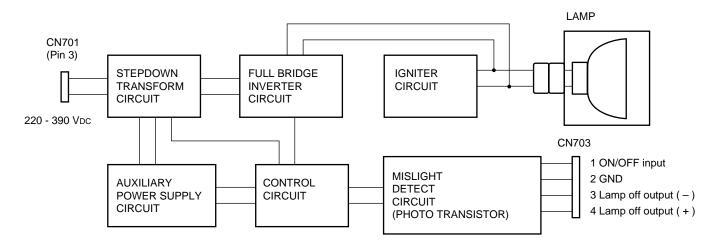

## 1. LAMP HIGH VOLTAGE POWER SUPPLY

The lamp high voltage power supply receives a DC220 to 390V (primary side) from the system power supply and provides a DC voltage (50 to  $70V_{DC}$  at ever turning on the lamp) to turn on the lamp. Fig. 2-1 shows the block diagram.

Fig. 2-1

The DC voltage is supplied to CN701 from the main power supply unit through an interlock switch (S023). This voltage becomes AC input x  $2\ddot{o} \ \overline{2}$  (= 340V for AC120V input) when the lamp is off. CN703 is a connector for the lamp on control signal input and lamp off control signal output. When +5V is applied to the ON/OFF input in the standby on, Q702 FET transistor turns on, igniter develops a high voltage pulse (13 to 18 kV), and the lamp starts to light up.

The pulse continues until the lamp turns on (for about 1 to 2s.). But if the lamp does not turn on, the OFF output is developed. Q702 goes off after the lamp turned on, the igniter circuit stops the operation, and the DC50 to 70V is applied to the lamp.

## SECTION III OPTICAL SYSTEM

#### 1. CONFIGURATION

|                    | No.            | Name                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|----------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | 17             | Metal halide<br>lamp                                            | Light source of the optical system. DC system,250W, short arc length 3mm.  To use light effectively in the tilt projection system, the light axis is arranged to face upward.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Lamp unit          | 16             | Elliptical reflector                                            | Elliptical reflector converges light emitted from the metal halide-lamp, thereby creating light beams parallel with light axis and illuminating the beams to the liquid crystal panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | 15             | Capacitor lens                                                  | Converges the parallel light beams from the reflector in direction of focal point and effectively transmits the beams through 1.3 inch liquid crystal panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | 14, 12         | Multi-lens                                                      | Multi-lens allows a circular beam light emitted from the light source to illuminate the square liquid crystal panel evenly, thus providing projected pictures with less brightness variation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    | 13             | Cold mirror                                                     | Visible light reflects at plane of incidence and goes to liquid crystal direction but infrared light and ultraviolet light penetrate, thus preventing undesired harmful light components from entering the liquid crystal panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | 10a~<br>10f    | Dichroic mirror                                                 | Only red light component of white light emitted from the lamp transmits through 10a and reflected by 10b, and enters liquid crystal panel (R). At the same time, only green of green and blue light components reflected is reflected by 10c and enters G-panel. While the blue light component transmits through and enters B-panel. Light transmitted through each liquid crystal synthesized by the dichroic mirror 10f.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | 5              | Field lens                                                      | Light transmitted through liquid crystal panel is converged in direction of focal point and effectively entered entrance pupil of the projection lens.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

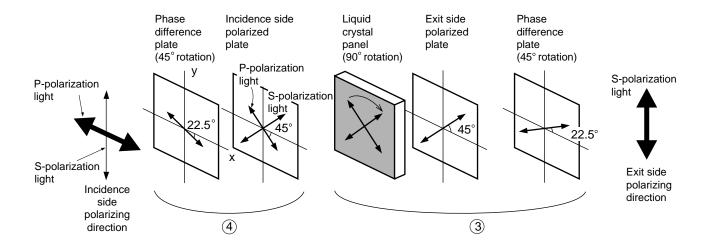

| Mirror<br>box unit | 4              | Phase difference<br>plate/ incidence<br>side polarized<br>plate | Spectral characteristics for the dichroic mirror depend on polarization directions of the light (P-polarization, S-polarization). To use the characteristics, a place the phase difference plate which possesses the characteristics to rotate the polarization direction of light by 45 degrees is provided. When the spectral characteristic of S-polarization is important, the phase of S-polarization is converted so that it matches the transmission axis of the incidence side polarization plate for the S-polarization light to pass the panel best.  On the other hand for the P-polarization, the phase is adjusted so that the P-polarization light passes the panel best.  In this unit, when the S-polarization characteristic takes effective for the G-light component and when the P-polarization characteristic takes effective for the R and B light components, thus improving the light transmission amount projected from the optical unit and the color reproduction characteristics.                                                                                                                                                                                                                                                                                                                               |

|                    | 3R<br>3G<br>3B | Liquid crystal<br>panel<br>(LCD)                                | Light exit side polarized plate and phase difference plate are put on the light exit plane. Polarization direction of transmission light rotates by 90 degrees when no signal voltage is applied, but a polarized plate has a characteristic which suppresses the rotation when a voltage is applied, To effectively use this characteristic, polarized plates, phase difference of polarized components transmitted through incidence side and exit side of which is 90 degrees, are located. That is, picture is displayed so that light transmits through most (white) when no signal voltage is applied and the light transmits through least (black) when a signal voltage is applied. Polarized light components transmitted through incidence side polarized plate is rotated by 45 degrees from Y axis in clockwise. This is to match aligning film of the liquid crystal panel for increasing efficiency of the light transmission.  Phase difference plate rotates the exit side polarized plate by 45 degrees in counterclockwise direction (that is, in the light polarizing direction of the transmitting light) to obtain S-polarization light. This operation is to increase effect of polarized screen because, generally speaking, transmission axis of polarized screen has the same direction as that of S-polarization. |

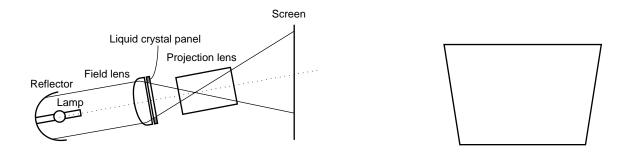

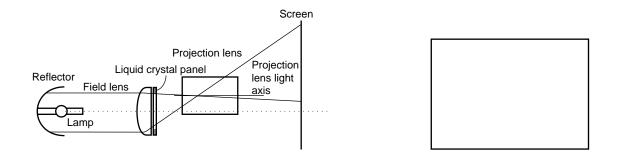

| Projection<br>lens | 1              | Projection lens                                                 | Projects pictures displayed on the liquid crystal at a wall, screen, etc. Light axis of the projection lens is located at upper side of center of the liquid crystal panel because of a tilt projection system employed. In a normal projection system, the projection screen is positioned at right angle to the unit. In this case, the unit body will disturb for persons to see the screen in practice. So, the projection will be directed upward, and this causes a trapezoidal distortion in the picture. To prevent this, the tilt projection system which allows the users to see the pictures projected without the trapezoidal distortion. (Figs. 3-4 and 3-5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Fig. 3-2 Polarizing direction at each part (G light components)

Fig. 3-3 Polarizing direction at each part (R/B light component)

(a) General projection system

(b) Picture by general projection system

Fig. 3-4 General projection system

(a) Tilt projection system

(b) Picture by tilt projection system

Fig. 3-5 Tilt projection system

## SECTION IV RGB DRIVE CIRCUIT

#### 1. OUTLINE

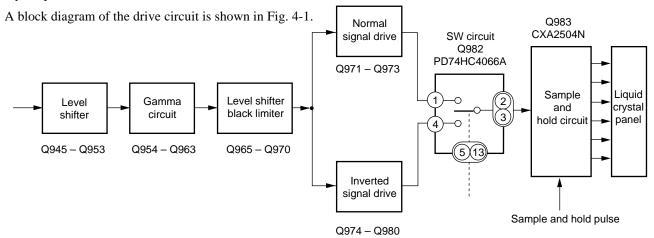

This circuit is described using G process as an example and composed of level shifter, gamma (9), black limiter, inverted signal amplifier, sample & hold circuit and liquid crystal panel.

Fig. 4-1

#### 2. CIRCUIT DESCRIPTION

The following description will be given assuming that  $V_{BE}$  of transistor is 0.7V.

#### 2-1. Level Shifter (Q945 – Q953)

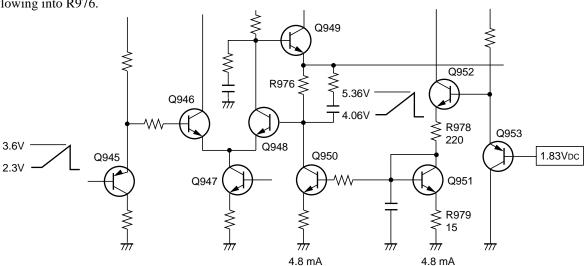

This circuit is composed of the emitter follower Q945, full feedback unit gain amplifier Q946 – Q950, and the current source circuit of sub bright for Q951 – Q953. The circuit operates to vary only the DC level of the input signal and develops the signal with only the DC level shifted from the input signal at Q949. The shift level is determined by the current flowing into R976.

When a triangular waveform of 2.3V - 3.6V shown in Fig. 4-2 is input, a triangular waveform of 3.0 - 4.3V appears at the base of Q946. At the same time, a triangular waveform of approx. 3.0V - 4.3V also appears at the base of Q948.

Assuming the sub brightness adjustment voltage at Q953 is  $1.83\,V_{DC}$ , a current of (1.83V-0.7V)/(220+15)=4.97 mA flows into Q951 and Q950, and this current also flows into R976. Therefore, the emitter voltage of Q949 develops 1.06V higher than the base voltage of Q948 as shown in the equation;  $4.8\,\text{mA}$  x 220W=1.06V. And the triangular waveform of 4.06V-5.36V appears at the emitter of Q949.

Fig. 4-2 Level shifter circuit

#### 2-2. Gamma (g) Circuit

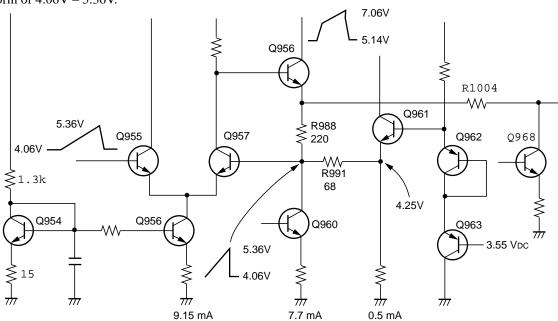

The circuit consists of a current source consisting of R983, R984, Q954, full feedback amplifier Q955 – Q960, the gain variation circuit Q961 – Q963 and R991. (The circuit including Q955 – Q963 is called the gamma circuit.)

A current of (12.7V-0.7V)/(1.3~kW+15W)=9.15~mA is flown into the current source for Q954 and the same current is also flown into Q956 (Q947). At the same time, a current of 9.15~mA x (15/20)=6.9~mA is flown into Q960.

The followings are described referring to Fig. 4-3.

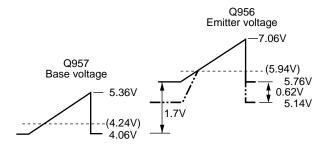

The signal from the level shifter is supplied to the base of Q955. If the device elements and currents of Q955 and Q957 are exactly the same, the base state of Q955 is same as that of Q957. However, Q955 and Q957 are not paired in their characteristics, the actual base state will be different. The base state of Q957 is described by referring to the triangular waveform of 4.06V - 5.36V.

When the base of Q963 develops 3.55 V<sub>DC</sub>, the emitter of Q961 develops 4.25 V<sub>DC</sub>. In the signal area where the base of Q963 is higher than 4.25 V, the current of 7.7 mA is flown into R988 because of Q961 turned off, and the emitter voltage of Q956 increases by amount of 1.7 V, 7.7 mA x 220 W = 1.7 V, from the base of Q957. As the base voltage of Q957 is close to 4.25 V, Q961 turns on and the current is flown into the collector of Q960 through R991.

When the base voltage of Q957 develops 4.06V, the current flowing into R991 is 2.8 mA, (4.25V - 4.06V)/68 = 2.8 mA. The current flowing into R998 decreases by that amount and the voltage shifting amount also decreases by the same amount,  $2.8 \text{ mA} \times 220\text{W} = 0.62\text{V}$ . The operation is shown in Fig. 4-4.

Fig. 4-3 Gamma circuit

Fig. 4-4 Gamma circuit operation

## 2-3. Level Shifter Circuit (0965 – 0968, R1044)

Q965-Q967 works as a current source. Assuming that the base voltage of Q965 is 1.76  $V_{DC},\,$  the current 4.2 mA is flown into Q967 and the same current also flown into Q968. The current and R1044 make a voltage drop and only the DC level is shifted.

#### 2-4. Black Limiter (Q969, Q970)

The black limiter is a switching circuit and its operation is as follows. When the base voltage of Q969 is higher than that of Q970, Q969 turns on and when the base voltage of Q969 is lower than that of Q970, Q969 turns off and Q970 turns on.

## 2-5. Inverted Signal Amplifiers (O974 – O981)

• Q974, Q975: Emitter follower

• Q976 – Q978: Inverted signal amplifier

• Q979 – Q981: Emitter follower

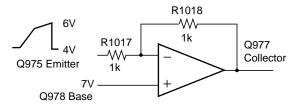

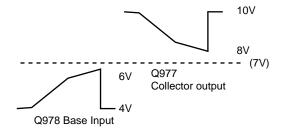

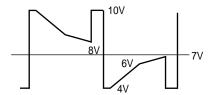

The op. amplifier is composed of Q976 – Q978. Q977 base accepts an inverted input and Q978 normal input. For easy understanding of the op. amplifier, an op. amplifier shown in Fig. 4-5 will be refferred.

Fig. 4-5

The output of Q977 is 7V x (1 + R1018/R1017) - 4V = 10V, so 7V x (1 + R1018/R1017) - 6V = 8V is output. (The constant of R1017 is assumed to 1 kW, in considering the internal emitter resistor of Q975.)

Accordingly, the output shown in Fig. 4-6 is obtained.

Fig. 4-6 Reverse output operation

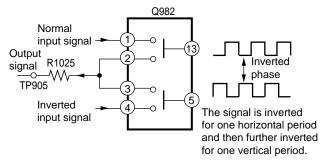

#### 2-6. Switch Circuit (Q982 µPD74HC4066A)

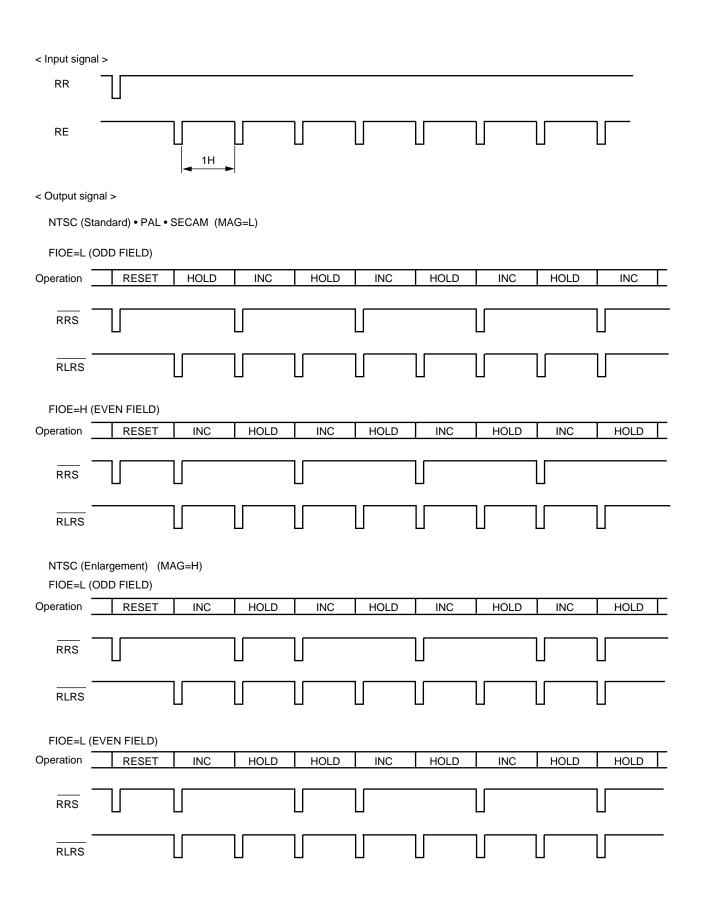

The normal and inverted signal outputs are switched for every horizontal and vertical period.

The signal is inverted for one horizontal period and then further inverted for one vertical period.

Fig. 4-7 SW circuit operation

Fig. 4-8

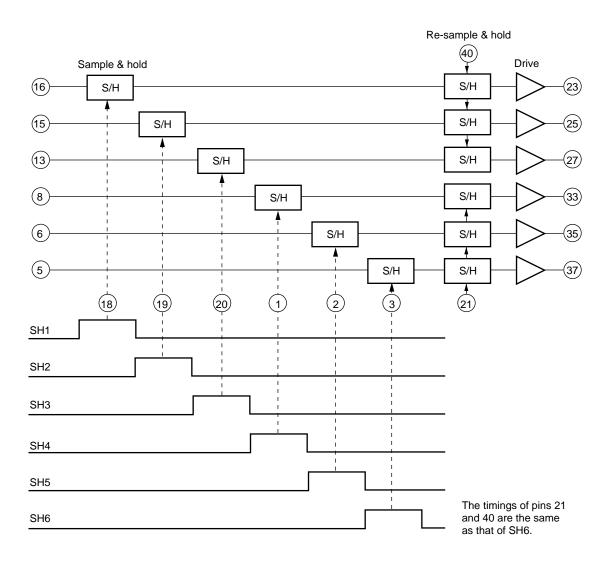

#### 2-7. Sample & Hold Circuit

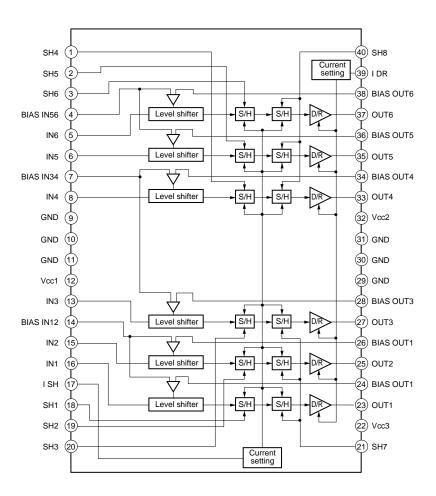

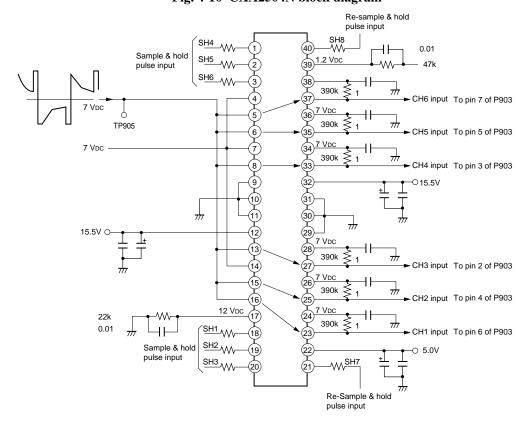

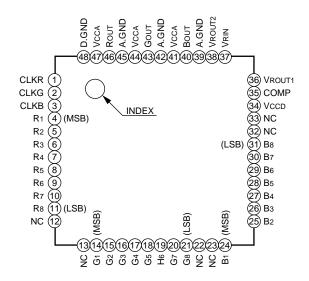

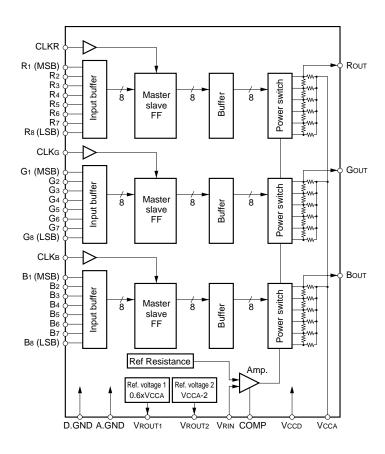

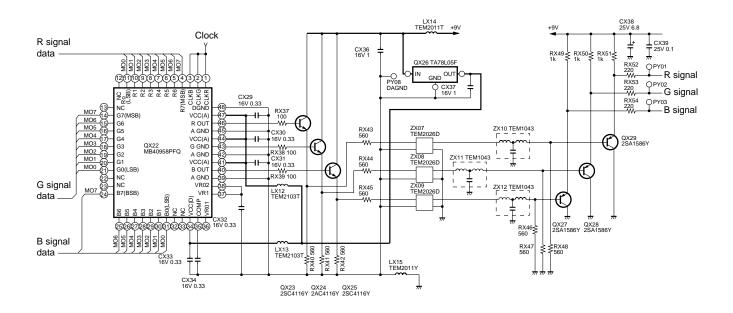

The block diagram of the circuit is shown in Fig. 4-10 and its connection diagram is shown in Fig. 4-11. As shown in the block diagram in Fig. 4-9, 6CH, each consisting of the level shifter, S/H (sample and hold) and driver circuits, are contained in CXA2504N.

Each sample & hold operation is carried out on pins 18, 19, 20, 1, 2 & 3 and the re-sample & hold operations for 6CH are carried out together on pins 21 and 40. This means that the serial data is converted to the parallel data and the LCD panel operation frequency is lowered.

Fig. 4-9 Sample & hold operation

Fig. 4-10 CXA2504N block diagram

Fig. 4-11 Peripheral circuit of sample & hold circuit

#### 2-8. LCD Panel

The LCD panel uses the active matrix panel with 3.3 cm in diagonal length and a built in driver made of the super thin film multi-crystal silicone transistor. Use of 3 panels enables to display in full color mode. The pixels are arranged in square form which is adequate for the data projection use. This realizes to display figures and characters clearly.

Also, use of a high luminance screen employing the advanced on-chip black matrix and a built-in cross-talk free circuit provides a high screen quality with less cross-talk.

The poly-silicone TFT high speed scanner is used and up/down and left/right inversion function is provided. Furthermore, use of 5V system interface circuit realizes a low voltage consumption for the timing and control signals.

#### 2-8-1. Features

- Number of dots displayed: 519,000 dots in diagonal length of 3.3 cm (1.3 type)

- High transparent ratio: 20%

- Built-in cross-talk free circuit

- High contrast ratio in normally white mode: 200 (Standard)

- Built-in H, V driver (Built-in input level conversion circuit, 5V driving possible)

- Up/down and left/right inversion display function

#### 2-8-2. Element component

- Number of dots: 832 (H) x 624 (V) = 519,168

- Active matrix panel with the driver using multi-crystal silicone transistors

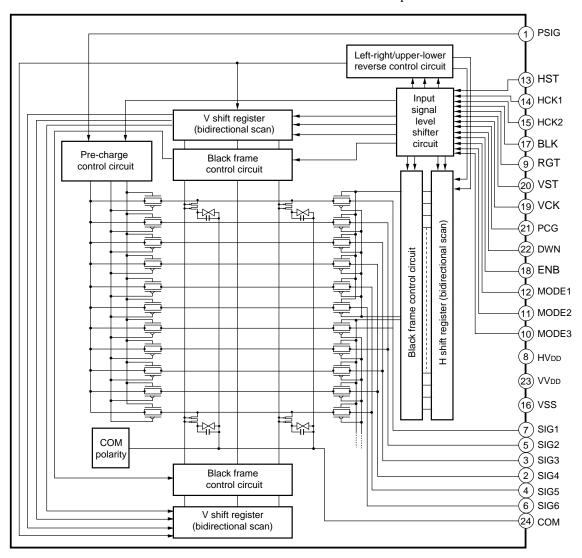

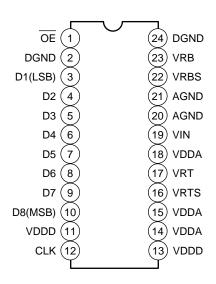

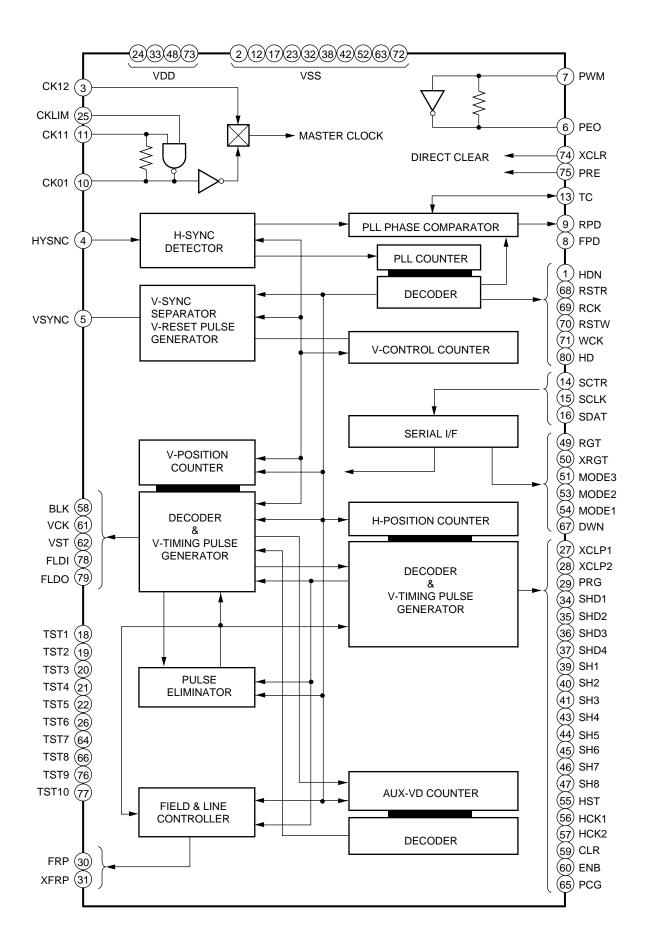

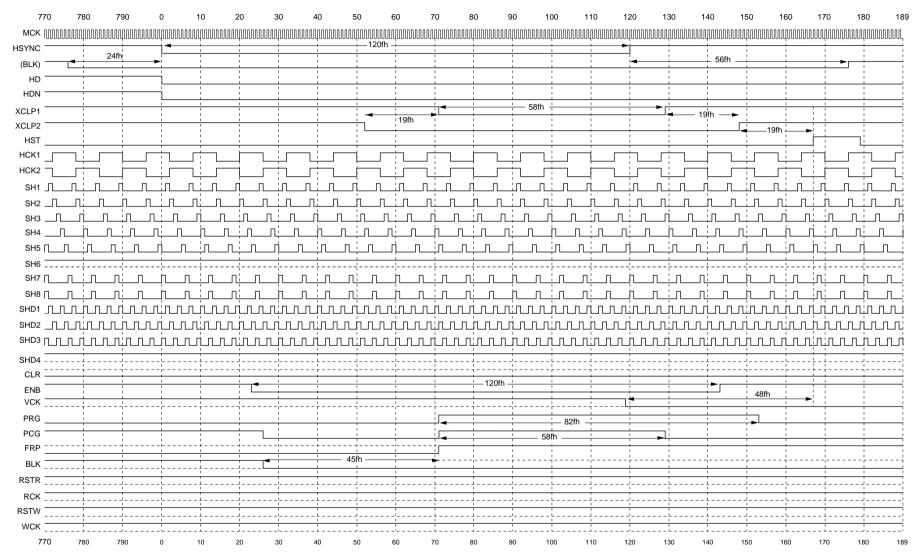

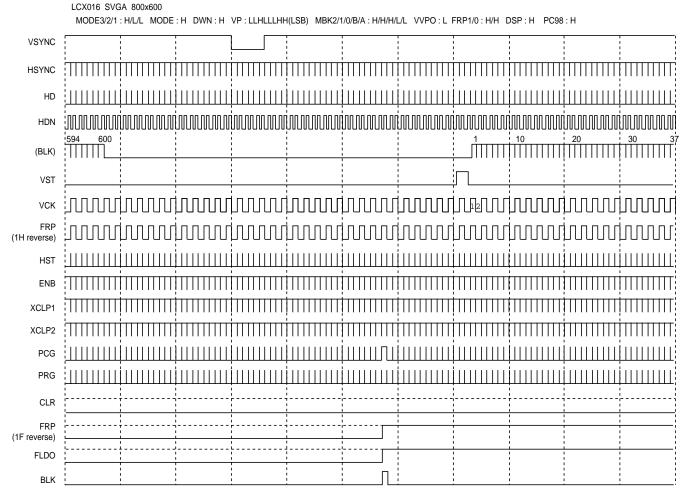

The block diagram of the LCD panel is shown in Fig. 4-12 and terminal description is in Table 4-1.

Fig. 4-12 Liquid crystal panel block diagram

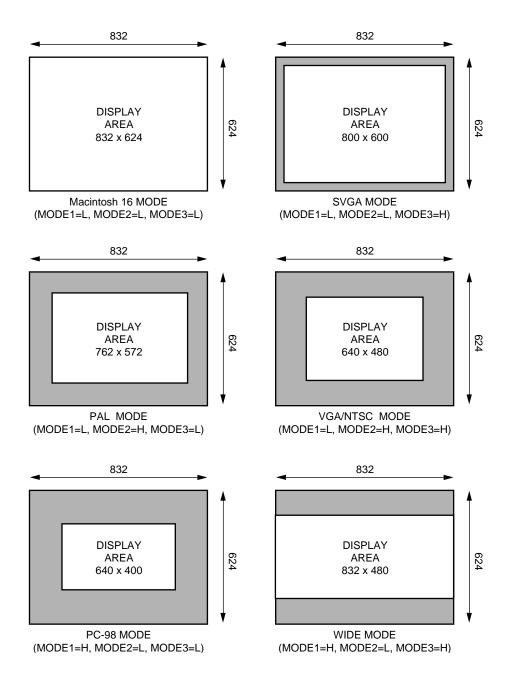

The liquid crystal panel is provided with a built in display area variable circuit inside the liquid crystal panel. It is possible to correspond with each signal of MAC16/SVGA/VGA/PC98/NTSC/WIDE/PAL. The mode switching described above is carried out owing to the signal developed at pins 10 to 12 of the display area switch input terminal as shown in Fig. 4-13. The area not displayed (shaded portions in Fig. 4-13) is written by PSIG signal of pin 1.

Fig. 4-13

Table 4-1 Liquid crystal panel terminal description

| Pin<br>No. | Symbol           | Description                                                                                       | Pin<br>No. | Symbol           | Description                                                                                        |

|------------|------------------|---------------------------------------------------------------------------------------------------|------------|------------------|----------------------------------------------------------------------------------------------------|

| 1          | PSIG             | Uniformity improvement signal input terminal                                                      | 13         | HST              | Start pulse input terminal for H shift resistor driving                                            |

| 2          | SIG4             | Video signal 4 input terminal to LCD panel, 7V center ± 4.5 V max.                                | 14         | HCK1             | Clock input terminal for H shift resistor driving                                                  |

| 3          | SIG3             | Video signal 3 input terminal to LCD panel                                                        | 15         | HCK2             | Clock input terminal for H shift resistor driving                                                  |

| 4          | SIG5             | Video signal 5 input terminal to LCD panel                                                        | 16         | V <sub>SS</sub>  | GND terminal for H, V drivers, GND                                                                 |

| 5          | SIG2             | Video signal 2 input terminal to LCD panel                                                        | 17         | BLK              | External frame display pulse input terminal                                                        |

| 6          | SIG6             | Video signal 6 input terminal to LCD panel                                                        | 18         | ENB              | Enable input terminal for gate selection pulse                                                     |

| 7          | SIG1             | Video signal 1 input terminal to LCD panel                                                        | 19         | VCK              | Clock input terminal for V shift resistor driving                                                  |

| 8          | HV <sub>DD</sub> | Power supply input terminal for H driver, 15.5V                                                   | 20         | VST              | Start pulse input terminal for V shift resistor driving                                            |

| 9          | RGT              | Driving direction input terminal for H shift resistor (H: Normal direction, L: Reverse direction) | 21         | PCG              | Uniformity improvement pulse input terminal                                                        |

| 10         | MODE3            | Display area SW 3 input terminal                                                                  | 22         | DWN              | Driving direction input terminal for V shift resist or (H: Normal direction, L: Reverse direction) |

| 11         | MODE2            | Display area SW 2 input terminal                                                                  | 23         | VV <sub>DD</sub> | Power supply input terminal for V driver, 15.5V                                                    |

| 12         | MODE1            | Display area SW 1 input terminal                                                                  | 24         | СОМ              | Counter power supply voltage input terminal for LCD panel, 6.6 V <sub>DC</sub>                     |

## SECTION V MICROCOMPUTER

#### 1. SYSTEM OUTLINE

The system microcomputer has features as shown below.

In considering easy maintenance for specification modification, etc. an external program ROM is employed. The program is also developed in considering use of structured notation, parts modularity, and multi filling system.

Major functions of the system microcomputer are as follows.

- (1) System control

- Power reset process

- Nonvolatile memory control process

- Remote control reception process

- RS-232C transmission and reception process

- · Status reading process

- On-screen display process

- (2) Normal control

- Power ON/OFF

- Input switch

- Sound volume control UP/DOWN

Menu UP/DOWN

Mute ON/OFF

Display ON/OFF

- Adjusting value reset

- Focus UP/DOWNZoom UP/DOWN

- (3) Adjustment control

- Video controls (high & low brightness ratio, brightness, color density, tint, sharpness)

- Panel adjustments (V position, H position, phase, clock)

- Projection adjustments (Front projection, front projection with ceiling mount, rear projection, rear projection with ceiling mount)

- Mode adjustments (Enlarge, wide, OSD mute, user fixing)

- Adjustment data saving process

- · Adjustment data default setting

- (4) Adjustment control at shipping

- Video sub adjustments (RGB gain)

- Drive adjustments (each item)

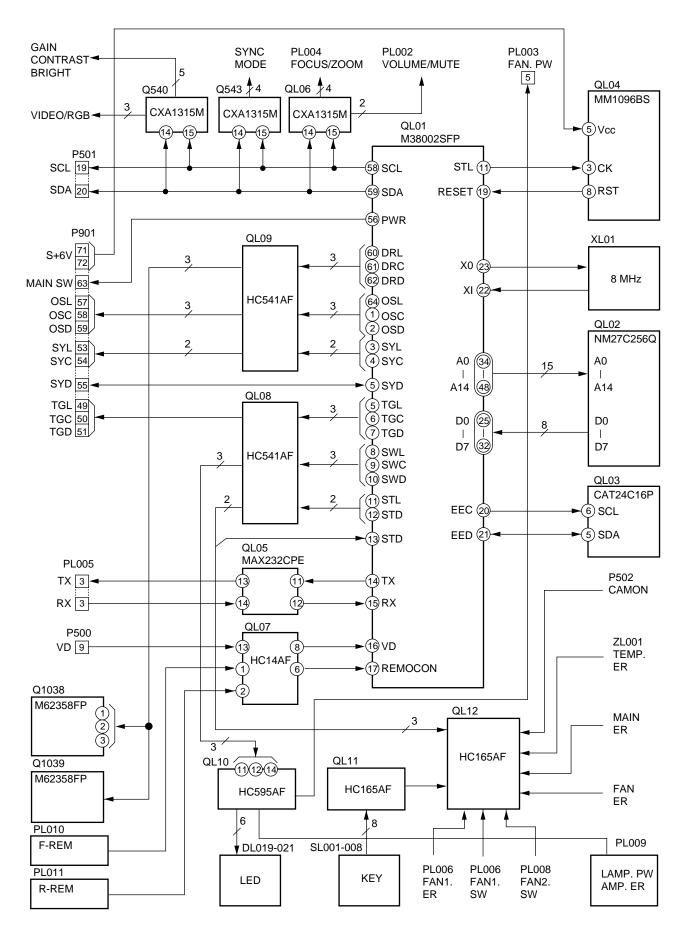

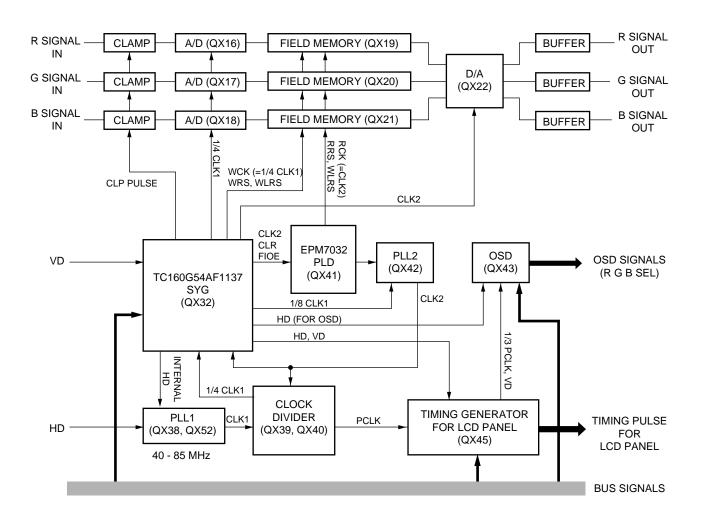

Fig. 5-1 shows the system block diagram.

Fig. 5-1 System block diagram

#### 2. SYSTEM MICROCOMPUTER

The system microcomputer QL01 employs an 8 bit microcontroller (M38002SFP).

In this system microcomputer, a program area provided inside the computer is not used but an external program ROM (QL02, NM27C256Q) is used.

This allows easy maintenance of the system when specification modification, bug correction, etc. will occur.

Table 5-1 shows the terminal function of the system microcomputer.

Table 5-1 Terminal function of the system microcomputer

| Pin<br>No. | Name              | Function                         | I/O | Pin<br>No. | Name            | Function                 | I/O  |

|------------|-------------------|----------------------------------|-----|------------|-----------------|--------------------------|------|

| 1          | OSD               | UPD6453 clock                    | 0   | 33         | A15             | Address for external ROM | 0    |

| 2          | SYL               | SYG load                         | 0   | 34         | A14             | Address for external ROM | 0    |

| 3          | SYC               | SYG clock                        | 0   | 35         | A13             | Address for external ROM | 0    |

| 4          | SYD               | SYG data                         | I/O | 36         | A12             | Address for external ROM | 0    |

| 5          | TGL               | CXD2442 load                     | 0   | 37         | A11             | Address for external ROM | 0    |

| 6          | TGC               | CXD2442 clock                    | 0   | 38         | A10             | Address for external ROM | 0    |

| 7          | TGD               | CXD2442 data                     | 0   | 39         | A9              | Address for external ROM | 0    |

| 8          | SWL               | HC595 latch                      | 0   | 40         | A8              | Address for external ROM | 0    |

| 9          | SWC               | HC595 clock                      | 0   | 41         | A7              | Address for external ROM | 0    |

| 10         | SWD               | HC595 data                       | 0   | 42         | A6              | Address for external ROM | 0    |

| 11         | STL               | HC165 load                       | 0   | 43         | A5              | Address for external ROM | 0    |

| 12         | STC               | HC165 clock                      | 0   | 44         | A4              | Address for external ROM | 0    |

| 13         | STD               | HC165 data                       | I   | 45         | А3              | Address for external ROM | 0    |

| 14         | TX                | RS-232C transmission data        | 0   | 46         | A2              | Address for external ROM | 0    |

| 15         | RX                | RS-232C reception data           | I   | 47         | A1              | Address for external ROM | 0    |

| 16         | VD                | Vertical flyback period pulse    | I   | 48         | A0              | Address for external ROM | 0    |

| 17         | RMC               | Remote controller reception data | I   | 49         |                 |                          | N. C |

| 18         | CNV <sub>SS</sub> | Operation mode setting           | I   | 50         |                 |                          | N. C |

| 19         | RESET             | External reset input             | I   | 51         |                 |                          | N. C |

| 20         | EEC               | CAT241C16 clock                  | 0   | 52         |                 |                          | N. C |

| 21         | EED               | CAT241C16 data                   | I/O | 53         |                 |                          | N. C |

| 22         | ΧI                | OSC input                        | I   | 54         | ONW             | External weight          | +5V  |

| 23         | X0                | OSC output                       | 0   | 55         |                 |                          | N. C |

| 24         | GND               | GND (0V)                         | I   | 56         | PWR             | Power switch             | 0    |

| 25         | D7                | Data for external ROM            | I   | 57         | V <sub>CC</sub> | Power supply (+5V)       | I    |

| 26         | D6                | Data for external ROM            | I   | 58         | SCL             | I <sup>2</sup> C clock   | 0    |

| 27         | D5                | Data for external ROM            | I   | 59         | SDA             | I <sup>2</sup> C data    | I/O  |

| 28         | D4                | Data for external ROM            | I   | 60         | DRL             | M62358 load              | 0    |

| 29         | D3                | Data for external ROM            | I   | 61         | DRC             | M62358 clock             | 0    |

| 30         | D2                | Data for external ROM            | ı   | 62         | DRD             | M62358 data              | 0    |

| 31         | D1                | Data for external ROM            | I   | 63         | OSL             | UPD6453 load             | 0    |

| 32         | D0                | Data for external ROM            | I   | 64         | osc             | UPD6453 clock            | 0    |

## 3. POWER SUPPLY RESET PROCESS

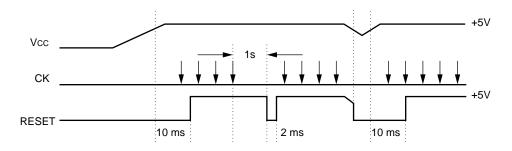

In the power supply reset process, a watch dog timer (MM1096BS) is used as a power supply reset IC (QL04) as shown in Fig. 5-1.

The reset IC (QL04) accepts a clock pulse signal for the watch dog timer which is sent from WDT terminal of the microcomputer, determines the microcomputer is in an abnormal status due to some reason if the clock signal does not exist for about 1s, and sends a reset signal to the RE-SET terminal of the system microcomputer (QL01).

Fig. 5-2 shows the MN1096BS reset timing diagram.

Fig. 5-2 MM1096BS reset timing diagram

## 4. NON-VOLATILE MEMORY PROCESS

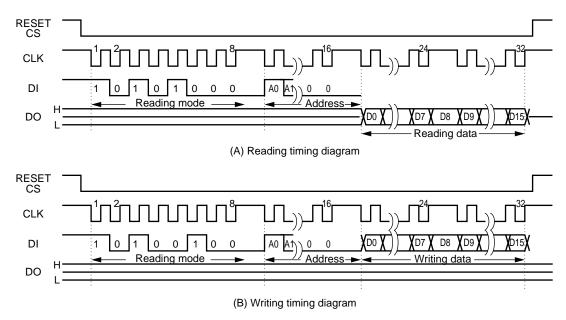

In the non-volatile memory process, data reading and writing for various adjustments are carried out on the non-volatile memory (QL03: CAT24C16) as shown in Fig. 5-1.

When the power (AC) is on, all the adjustment data are read out by the system microcomputer (QL01) at the timing shown in the read out timing diagram of Fig. 5-3 (A), thereby realizing the previous status.

When saving the data, all the adjustment data are written by the system microcomputer (QL01) at the timing shown in the timing diagram of Fig. 5-3 (B), thereby keeping the current status.

However, if a failure (such as power interruption due to lightening, etc.) occurs during the adjustment data writing, a data error may occur. If the data is determined as incorrect, the initial data memorized on the system microcomputer (QL01) is read out and stored on the non-volatile memory.

Fig. 5-3 Non-volatile memory timing diagram

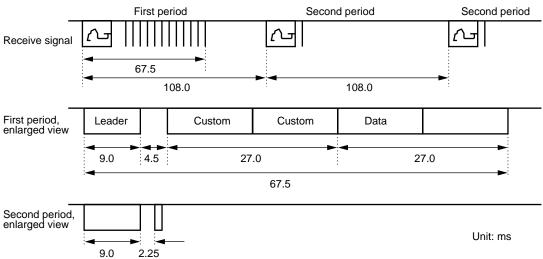

#### 5. REMOTE CONTROL RECEPTION PROCESS

In the remote control reception process, a remote control unit (CT-9888) connected to the remote control terminal emits a remote control signal and a remote control signal receive section (ZL002) on the front panel or a remote control signal receive section (ZL003) on the rear panel decodes the signal.

Each remote control signal decoded is mixed through the connectors of PL010 or PL011 and fed to the system microcomputer (QL01) through a buffer QL07 (MC74 HC14AF).

Fig. 5-4 shows the remote control signal reception timing diagram.

Fig. 5-4 Remote control signal reception timing diagram

## 6. RS-232C TRANSMIT/RECEIVE PROCESS

In the RS-232C transmit/receive process, an RS-232C signal entered through the RS-232C connector (D-SUB 9P) on the rear panel is decoded in the RS-232C interface (QL05: MAX232CPE), and fed to the system microcomputer (QL01) through PL005.

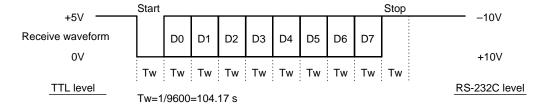

Fig. 5-5 shows the RS-232C signal timing diagram.

$Communication\ conditions: 9600\ pds,\ non-polarity,\ 8bits\ length,\ 1\ stop$

Fig. 5-5 RS-232C signal timing diagram

#### 7. STATUS READ PROCESS

In the status read process, two data fetch ICs, QL11, QL12 (MC74HC165AF) as shown in Fig. 5-1, read the status.

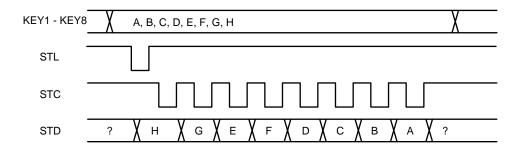

Fig. 5-6 shows a data fetch timing diagram.

QL11 reads panel key status and QL12 does various status. Table 5-2 shows the contents of the status read signals and

the logic.

Fig. 5-6 Data fetch timing diagram

Table 5-2 Contents of the status read signals and the logic

| Signal name | Α              | В                | С              | D            | E           | F        | G        | Н          |

|-------------|----------------|------------------|----------------|--------------|-------------|----------|----------|------------|

| Pin No.     | 11             | 12               | 13             | 14           | 3           | 4        | 5        | 6          |

| QL11        | ON/<br>STANDBY | MENU<br>( DOWN ) | MENU<br>( UP ) | VOL/ADJ( - ) | VOL/ADJ (+) | INPUT    | AUX1     | AUX2       |

| (L)         | ON             | ON               | ON             | ON           | ON          | ON       | ON       | ON         |

| (H)         | OFF            | OFF              | OFF            | OFF          | OFF         | OFF      | OFF      | OFF        |

| QL12        | FAN1. ER       | FAN1. SW         | FAN2. ER       | MAIN. ER     | LAMP. ER    | FAN. ER  | TEMP. ER | CAMON      |

| (L)         | Abnormal       | Normal           | Abnormal       | Abnormal     | Abnormal    | Abnormal | Normal   | Camera Yes |

| (H)         | Normal         | Abnormal         | Normal         | Normal       | Normal      | Normal   | Abnormal | Camera Yes |

#### 8. STATUS DISPLAY PROCESS

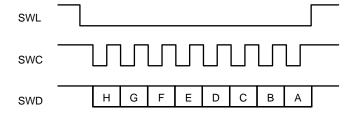

In the status display process, a status display IC QL10 (MC74HC595AF) shown in Fig. 5-1 displays the status.

Fig. 5-7 shows the data display timing diagram.

Table 5-3 shows the contents of the status display signals and the logic.

Fig. 5-7 Data display timing diagram

Table 5-3 Contents of the status display signals and the logic

| Signal name | QA          | QB            | Q             | QD           | QE            | QF              | G       | QH       |

|-------------|-------------|---------------|---------------|--------------|---------------|-----------------|---------|----------|

| Pin No.     | 15          | 1             | 2             | 3            | 4             | 5               | 6       | 7        |

| QL10        | ON<br>(red) | ON<br>(green) | LAMP<br>(red) | LAMP (green) | TEMP<br>(red) | TEMP<br>(green) | FAN. PW | LAMP. PW |

| (L)         | LED off     | LED off       | LED off       | LED off      | LED off       | LED off         | OFF     | OFF      |

| (H)         | LED on      | LED on        | LED on        | LED on       | LED on        | LED on          | ON      | ON       |

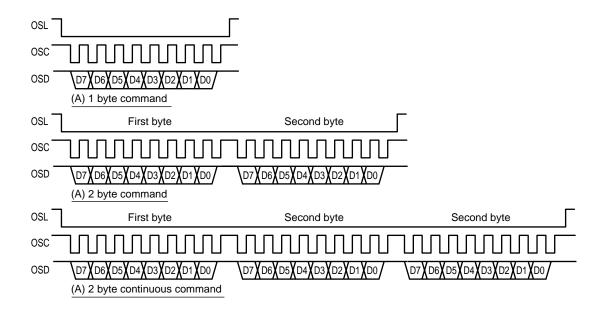

#### 9. ON-SCREEN DISPLAY PROCESS

In the on-screen display process, control signals are supplied to the OSD display IC QX43 (mPD6453) through P901, and the OSD display IC generates character display signals at the timing determined by VD, HD and clock supplied to the IC separately.

Fig. 5-8 shows the timing diagram for the on-screen control signals.

Fig. 5-8 Timing diagram for on-screen control signals

## 10. VIDEO MODE FETCH PROCESS

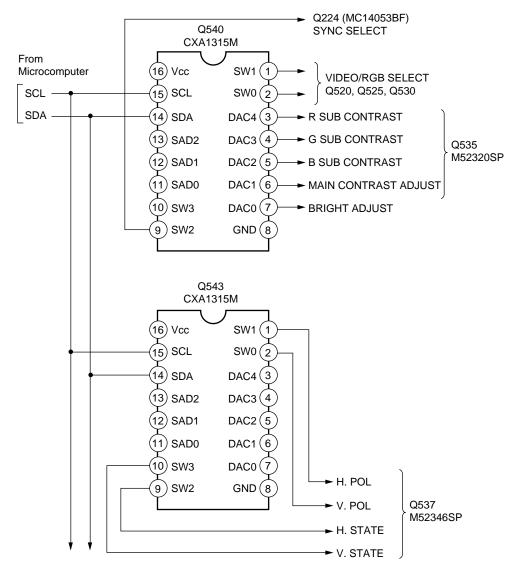

In the video mode fetch process, a status fetch IC Q543 (CXA1315M) fetches the status in the read mode of I<sup>2</sup>C bus (Custom: \$45).

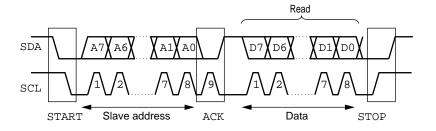

Fig. 5-9 shows the  $I^2C$  bus read timing diagram. Table 5-4 shows the contents of the video mode signals and the logic.

Table 5-4

Contents of the video mode signals and the logic

| Signal<br>name | SW0 SW1           |                      | SW2      | SW3      |  |

|----------------|-------------------|----------------------|----------|----------|--|

| Pin No.        | 2                 | 2 1                  |          | 10       |  |

| Q543           | V. POL            | H. POL               | H. STATE | V. STATE |  |

| (L)            | Positive polarity | Positive polarity    | No       | No       |  |

| (H)            | Negative polarity | Negative<br>polarity | Yes      | Yes      |  |

Fig. 5-9 I<sup>2</sup>C bus read timing diagram

## 11. VIDEO SYSTEM CONTROL PROCESS

In the video system control process, control signals are supplied to various video system process ICs through P501.

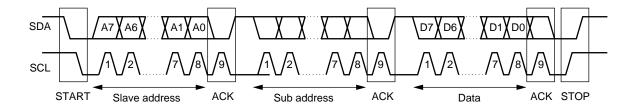

Fig. 5-10 shows the  $I^2C$  bus timing diagram and table 5-5 shows the contents of process in each kind of IC.

Table 5-5 Contents of process in each kind of IC

| Part No. | Type name               | Contents of process                                                                       |

|----------|-------------------------|-------------------------------------------------------------------------------------------|

| Q540     | CXA1315M (Custom: \$42) | Brightness, contrast, RGB gain, Video/RGB input switching                                 |

| Q200     | TA1218N (Custom: \$90)  | Input signal (Video/Audio), Video/S terminal input                                        |

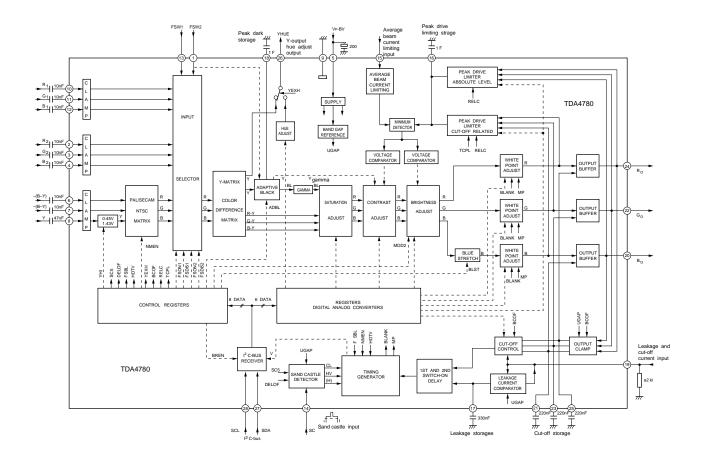

| Q201     | TC9090N (Custom: \$8A)  | Color signal process (3D Y/C separation)                                                  |

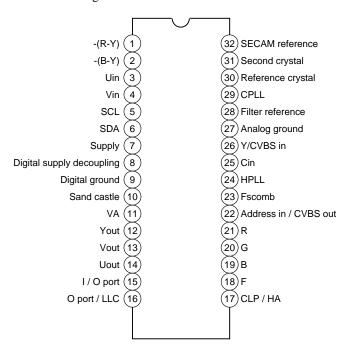

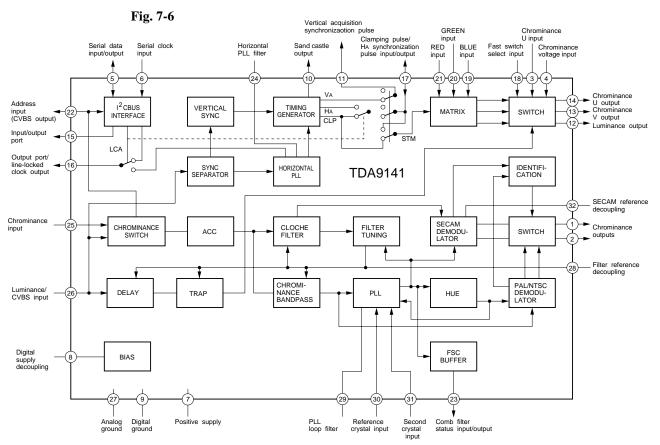

| Q220     | TDA9141 (Custom: \$8A)  | Sync detection process (Custom: \$8B), Signal kinds identification (NTSC/PAL/SECAM, etc.) |

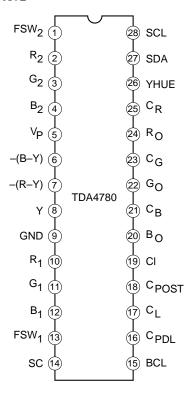

| Q223     | TDA4780 (Custom: \$88)  | Video control (Color density, tint)                                                       |

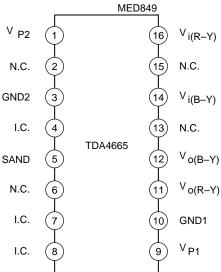

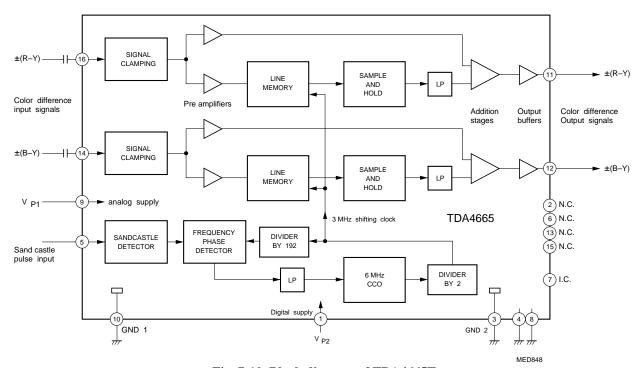

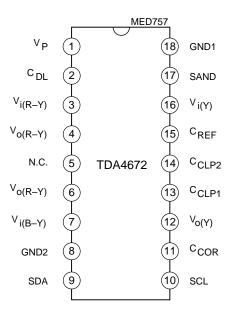

| Q222     | TDA4672 (Custom: \$88)  | Video control (Sharpness control)                                                         |

Fig. 5-10 I<sup>2</sup>C bus timing diagram

## 12. PANEL SYSTEM CONTROL PROCESS

The panel system control process supplies various control signals to the panel system control ICs through P901.

Table 5-6 shows the contents of process in each kind of IC.

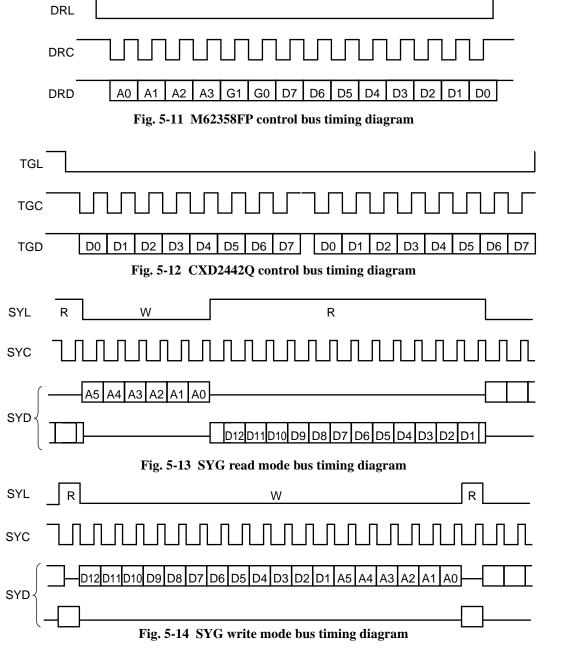

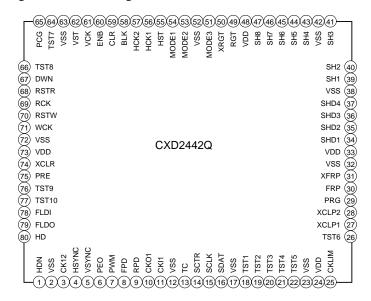

Fig. 5-11 shows the M62358FP control bus timing diagram, Fig. 5-12 does the CXD2442Q control bus timing diagram, Fig. 5-13 does the SYG read mode bus timing diagram and Fig. 5-14 does the SYG write mode bus timing diagram.

Table 5-6 Contents of process in each kind of IC

| Part No.       | Type name           | Contents of process                                                                                                       |  |  |  |  |

|----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Q1038<br>Q1039 | M62358FP            | Panel drive process                                                                                                       |  |  |  |  |

| QX45           | CXD2442Q            | Screen position control (V position , H position , sample phase) Panel display control (Projection, attribution, etc.)    |  |  |  |  |

| QX32           | SYG (TC160G54F-113) | Screen process control process (sample frequency),<br>Various screen display process (position, frame, attribution, etc.) |  |  |  |  |

#### 13. VARIOUS DISPLAY MODES

In this system, various LED display patterns are provided in relation to the display modes shown in Table 5-7. Operations from AC on to power on and power off will be given below.

Data of the non-volatile memory are checked at the AC on, and all the LED are turned on in red in the initial use. In second or later use, all the LEDs are turned on in green and the unit enters the standby status.

In the standby status, only the STANDBY/ON LED is turned on in orange, and the main power is off and the lamp power is also off.

When the power is on by pressing the STANDBY/ON key, the unit enters a normal status in passing through following processes.

- 1. The main power is on, and STANDBY/ON LED turns on in green.

- 2. The lamp power is on, and LAMP LED blinks in green for about 3s.

- 3. With the lamp turned on, LAMP LED turns on in green and the unit enters the normal status.

- 4. If the lamp does not turn on, STANDBY/ON LED turns on in orange, and the LAMP LED blinks for about 1 min. and then the unit returns to the standby status.

In the normal status, STANDBY/ON LED and the LAMP LED are turned on in green, and the main power and the lamp power are turned on.

When the power is turned off by pressing the STANDBY/ON key, the unit enters the standby status in passing through following processes.

- When the lamp power is turned off, STANDBY/ON LED turns on in orange.

- 2. The LAMP LED blinks in green for about 1 min. For this period the lamp can not be turned on again by the STANDBY/ON key.

- When blinking of the LAMP LED stops, only the STANDBY/ON LED turns on in orange. After this the lamp can be turned on again by the STANDBY/ ON key.

- 4. Moreover, the fan works for about 2 min. to lower temperature of the unit. For this period the main power is kept turning on.

- 5. When the main power turns off, the fan also stops and returns to the standby status.

If an error occurs due to some causes, the STANDBY/ON LED turns on in red, and the error information is kept in the display status of the LAMP and TEMP LEDs. When the error is detected, the unit enters the standby status after cooling down process for about 2 min. In this case, if the error status continues, the error display is also kept and any key entry is not accepted.

For the error due to the over time of the lamp-on time, the error is not released until the internal timer is reset (booting the system by turning the AC on with [–], [+], and [IN-PUT] keys pressed at the same time) after replacement of the lamp.

| Tuble of Tub |         |          |                               |                                      |                               |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-------------------------------|--------------------------------------|-------------------------------|--|--|--|--|

| ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LAMP    | TEMP     | Contents                      | Status                               | Remedy                        |  |  |  |  |

| Χ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Х       | Х        | Standby power abnormal        | normal at AC on Repair               |                               |  |  |  |  |

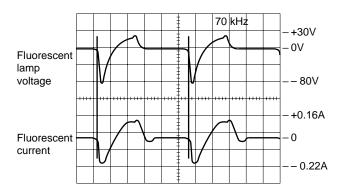

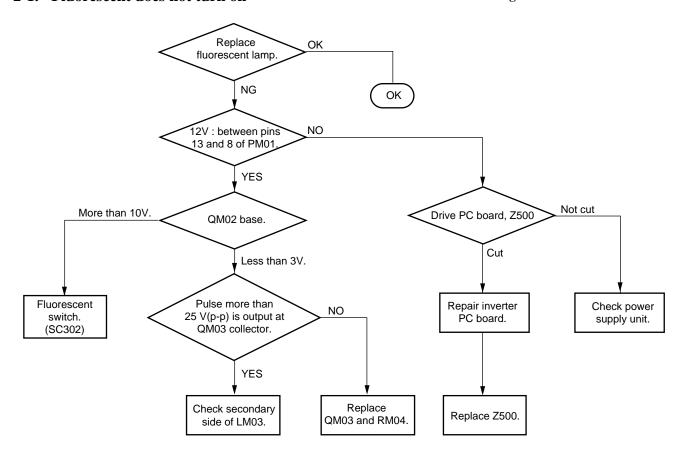

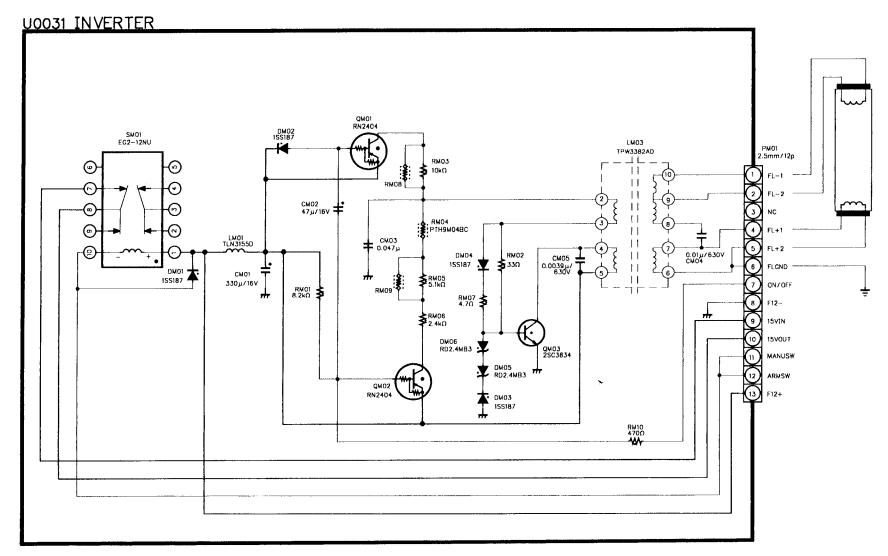

| Green                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Green   | Green    | Non-volatile memory OK        | at AC on                             | Normal                        |  |  |  |  |