## **Instruction Manual**

# **Tektronix**

TLA7PG2

Pattern Generator Probes

071-1017-01

This document supports Tektronix Logic Analyzer Family Software Version 4.1 and Tektronix Pattern Generator Software Version 1.3 and above.

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries prior to performing service.

www.tektronix.com

Copyright © Tektronix, Inc. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that the products that it manufactures and sells will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If a product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

|                  | General Safety Summary                                                                                                                                 | •                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                  | Service Safety Summary  Related Documentation  Contacting Tektronix                                                                                    | vi<br>iz                   |

| Operating Basics |                                                                                                                                                        |                            |

|                  | Product Description Probe Lead Sets and Cables Connecting the Standard Probes Connecting the P6475 Probe                                               |                            |

| Reference        |                                                                                                                                                        |                            |

|                  | Probe Connectors and Signal Names Probe Overview Probe Dimensions P6475 Installation Requirements Input/Output Circuits Timing Diagrams Specifications | 15<br>17<br>18<br>22<br>25 |

| Maintenance      |                                                                                                                                                        |                            |

|                  | Functional Check Inspection and Cleaning Static Discharge Information Configuring Probes Repackaging                                                   | 4:<br>4:<br>4:<br>4:       |

# **List of Figures**

| Figure 1: Standard probe, lead sets, and probe cable       | 2  |

|------------------------------------------------------------|----|

| Figure 2: P6475 variable probe, lead sets, power cord,     |    |

| and probe cable                                            | 3  |

| Figure 3: P6470 and P6474 output connector pin assignments | 7  |

| Figure 4: P6471 output connector pin assignments           | 7  |

| Figure 5: P6472 output connector pin assignments           | 8  |

| Figure 6: P6473 output connector pin assignments           | 8  |

| Figure 7: P6475 output connector pin assignments           | 8  |

| Figure 8: Strobe output pulse pattern                      | 11 |

| Figure 9: P6475 Variable probe output pulse pattern        | 11 |

| Figure 10: P6475 CH6 output example                        | 12 |

| Figure 11: P6475 CH6 output mode pulse patterns            | 13 |

| Figure 12: P6470, P6471, P6472, P6473 and P6474            |    |

| probe dimensions                                           | 15 |

| Figure 13: P6475 Variable probe dimensions                 | 16 |

| Figure 14: P6470 input/output circuit                      | 18 |

| Figure 15: P6471 input/output circuit                      | 19 |

| Figure 16: P6472 input/output circuit                      | 20 |

| Figure 17: Signaling sense                                 | 21 |

| Figure 18: P6474 input/output circuit                      | 22 |

| Figure 19: Clock and strobe timing diagram                 | 22 |

| Figure 20: P6470, P6472, P6473, and P6474 inhibit          |    |

| timing diagram                                             | 23 |

| Figure 21: P6470, P6472, P6473, and P6474 external event   |    |

| for inhibit timing diagram                                 | 23 |

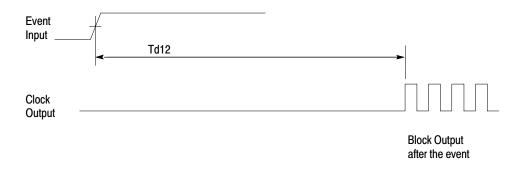

| Figure 22: External event for jump timing diagram          | 23 |

| Figure 23: External event for half channel advance         |    |

| timing diagram                                             | 24 |

| Figure 24: External event for full channel advance         |    |

| timing diagram                                             | 24 |

| Figure 25: External event for delay to data output         |    |

| for advance diagram                                        | 24 |

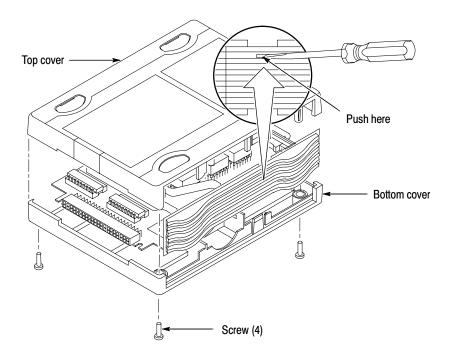

| Figure 26: Removing the standard probe cover     | 46 |

|--------------------------------------------------|----|

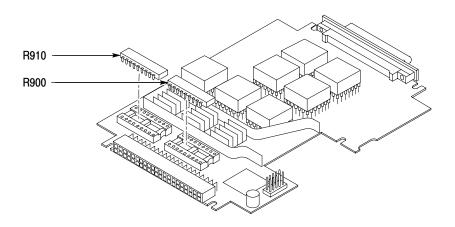

| Figure 27: P6470 series termination resistors    | 47 |

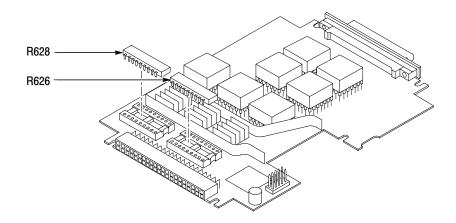

| Figure 28: P6474 series termination resistors    | 48 |

| Figure 29: P6472 PECL and LVPECL jumper position | 48 |

## **List of Tables**

| Table 1: Inputs and outputs of pattern generator probes | 9  |

|---------------------------------------------------------|----|

| Table 2: P6475 Variable probe installation requirements | 17 |

| Table 3: P6470 TTL/CMOS probe                           | 25 |

| Table 4: P6471 ECL probe                                | 28 |

| Table 5: P6472 PECL/LVPECL probe                        | 30 |

| Table 6: P6473 LVDS probe                               | 31 |

| Table 7: P6474 LVCMOS probe                             | 34 |

| Table 8: P6475 Variable probe                           | 37 |

| Table 9: Power Supply (P6475 only)                      | 42 |

| Table 10: Atmospherics                                  | 42 |

| Table 11: Dynamics characteristics (P6470, P6471,       |    |

| P6472, P6473, P6474)                                    | 42 |

| Table 12: Dynamics characteristics (P6475)              | 43 |

| Table 13: Probe cables                                  | 43 |

| Table 14: Twisted lead set                              | 43 |

| Table 15: Certifications and compliances for P6475      | 43 |

| Table 16: P6470 series termination resistors            | 47 |

## **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the *General Safety Summary* in other system manuals for warnings and cautions related to operating the system.

#### To Avoid Fire or Personal Injury

**Use Proper Power Cord.** Use only the power cord specified for this product and certified for the country of use.

**Ground the Product.** These products (P6470, P6471, P6472, P6473, and P6474) are indirectly grounded through the grounding conductor of the mainframe power cord. The P6475 is directly grounded through the grounding conductor of the probe power cord. To avoid electric shock, the grounding conductor must be connected to earth ground. Before making connections to the input or output terminals of the product, ensure that the product is properly grounded.

**Observe All Terminal Ratings.** To avoid fire or shock hazard, observe all ratings and markings on the product. Consult the product manual for further ratings information before making connections to the product.

**Do Not Operate Without Covers.** Do not operate this product with covers or panels removed.

**Use Proper Fuse.** Use only the fuse type and rating specified for this product.

**Avoid Exposed Circuitry.** Do not touch exposed connections and components when power is present.

**Do Not Operate With Suspected Failures.** If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

**Keep Product Surfaces Clean and Dry.**

**Provide Proper Ventilation.** Refer to the manual's installation instructions for details on installing the product so it has proper ventilation.

#### **Symbols and Terms**

**Terms in this Manual.** These terms may appear in this manual:

**WARNING.** Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

**Terms on the Product.** These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

**Symbols on the Product.** The following symbols may appear on the product:

Protective Ground

# **Service Safety Summary**

Only qualified personnel should perform service procedures. Read this *Service Safety Summary* and the *General Safety Summary* before performing any service procedures.

**Do Not Service Alone.** Do not perform internal service or adjustments of this product unless another person capable of rendering first aid and resuscitation is present.

**Disconnect Power.** To avoid electric shock, switch off the instrument power, then disconnect the power cord from the mains power.

**Use Care When Servicing With Power On.** Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

General Safety Summary

## **Preface**

This document provides information on using and servicing the TLA7PG2 probes.

#### **Related Documentation**

In addition to these probe instructions, the following documentation is available for your Tektronix Logic Analyzer Family:

- The *TLA7PG2 Pattern Generator and Probes Service Manual* provides service information for the pattern generator and pattern generator probes.

- The *Tektronix Logic Analyzer Family User Manual* provides overall user information for the Tektronix logic analyzers.

- The online help provides information for the probes and pattern generator user interfaces and the Pattern Generator Programmatic Interface (PPI).

- A series of instruction manuals for microprocessor support provides operating and service instructions for the individual microprocessor support packages that are available for use with the logic analyzer.

- Probe instructions accompany the logic analyzer modules to provide operating and service information.

- The *Tektronix Logic Analyzer Family Training Manual* provides training exercises to help you learn key features of the logic analyzer. The training manual is designed to be used with the TLA7QS training board.

- A series of service manuals are available that provide performance verification procedures and board-level service information for major components of the logic analyzer.

## **Contacting Tektronix**

Phone 1-800-833-9200\*

Address Tektronix, Inc.

Department or name (if known) 14200 SW Karl Braun Drive

P.O. Box 500 Beaverton, OR 97077

USA

Web site www.tektronix.com

Sales support 1-800-833-9200, select option 1\*

Service support 1-800-833-9200, select option 2\*

**Technical support** Email: TechSupport@tektronix.com

1-800-833-9200, select option 3\*

1-503-627-2400

6:00 a.m. - 5:00 p.m. Pacific time

<sup>\*</sup> This phone number is toll free in North America. After office hours, please leave a voice mail message.

Outside North America, contact a Tektronix sales office or distributor; see the Tektronix web site for a list of offices.

## **Operating Basics**

This section provides a brief description of the TLA7PG2 probes and information on connecting the probes from the pattern generator module to the target system.

### **Product Description**

The pattern generator probes provide multichannel signals to simulate signals in a test environment. Following are descriptions of the probes discussed in this manual:

#### P6470 TTL/CMOS

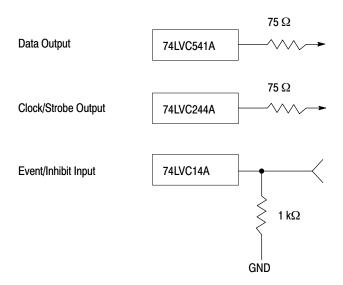

The P6470 provides TTL or CMOS signals to the target system and contains 16 data outputs, 1 clock output, and 1 strobe output. The  $V_{cc}$  output driver is adjustable from 2.0 V to 5.5 V. Figure 14 on page 18 shows the P6470 input/output circuit.

The P6470 probe comes standard with 75  $\Omega$  termination resistors packs. You can change the resistor packs to provide impedance matching for the target system. Refer to *Removing the Probe Cover* on page 46 and *Changing the Series Termination Resistors* on page 47.

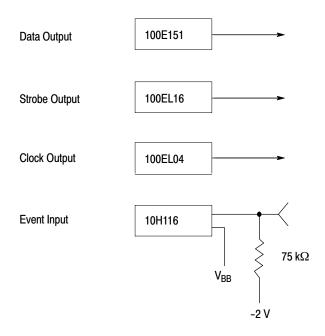

#### P6471 ECL

The P6471 ECL pattern generator probe provides ECL signals to the target system and contains 16 data outputs, 1 clock output, and 1 strobe output. Figure 15 on page 19 shows the P6471 input/output circuit.

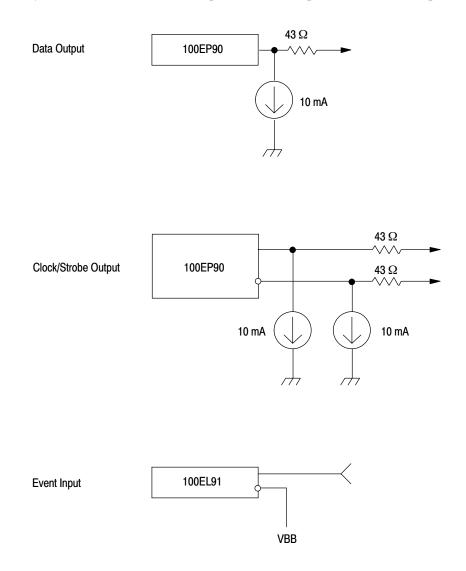

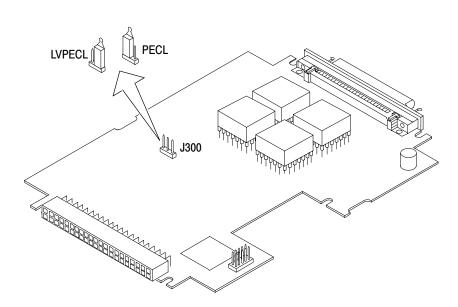

#### P6472 PECL/LVPECL

The P6472 provides PECL/LVPECL signals to the target system and contains 8 data outputs, 1 clock output, and 1 strobe output. You can select PECL or LVPECL by moving a jumper in the probe. See *Configuring the P6472 for PECL or LVPECL* on page 48. Figure 16 on page 20 shows the P6472 input/output circuit.

#### **P6473 LVDS**

The P6473 provides LVDS signals to the target system and contains 16 data outputs, 1 clock output, and 1 strobe output. All inputs and outputs are LVDS level.

#### P6474 LVCMOS

The P6474 provides LVCMOS signals to the target system and contains 16 data outputs, 1 clock output and 1 strobe output. Figure 18 on page 22 shows the P6474 input/output circuit.

The  $V_{cc}$  of the output driver is adjustable from 1.2 V to 3.3 V.

The P6474 comes standard with 75  $\Omega$  termination resistors packs. You can change the resistor packs to provide impedance matching for the target system. Refer to *Removing Probe the Cover* on page 46 and *Changing the Series Termination Resistors* on page 47.

#### P6475 Variable

The P6475 provides logic family signals such as ECL, TTL/CMOS, and PECL/LVPECL and contains 8 data outputs and one clock output. The P6475 also supports variable delay (0 to 50 ns) for two channels (CH6 and CH7).

When using the P6475 probe with a P6470 (TTL/CMOS), P6473 (LVDS), or P6474 (LVCMOS) probe, it is recommended that you use a Time Alignment Cable (P/N 012-A223-00) in conjunction with the TLA7PG2 Pattern Generator Module. The Time Alignment Cable ensures that the P6475 and the P6470, P6473, or P6474 probes are time aligned and can be used together. Please order one Time Alignment Cable (P/N 012-A223-00) for each P6470, P6473, and P6474 probe.

#### **Probe Lead Sets and Cables**

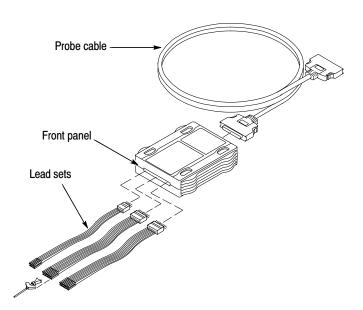

Figure 1 shows a typical pattern generator probe with the lead sets and probe cable. The probe cable is included with the TLA7PG2 pattern generator module. Refer to *Probe Connectors and Signal Names*, beginning on page 7, for probe connector information.

Figure 1: Standard probe, lead sets, and probe cable

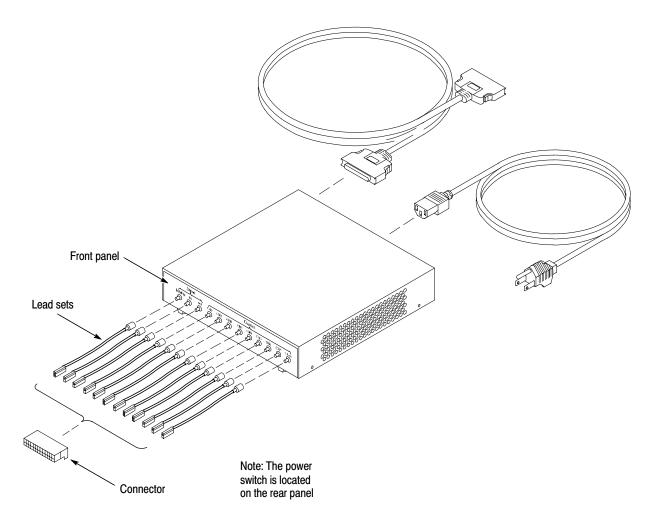

Figure 2 shows the P6475 variable probe, lead sets and probe cable. The probe cable is included with the TLA7PG2 pattern generator module.

Figure 2: P6475 variable probe, lead sets, power cord, and probe cable

## **Connecting the Standard Probes**

To connect the probes to the logic analyzer and to the target system, do the following steps:

- 1. Power off the logic analyzer and the target system before connecting the pattern generator probes.

- **2.** Connect the lead sets to the target system.

- **3.** Connect the standard probe as shown in Figure 1. The probe cable is reversible. You can connect the probe cable in either direction.

**4.** Connect the probe to the pattern generator module on the logic analyzer.

**CAUTION.** To prevent damage to the pattern generator module or probe, do not connect or disconnect the pattern generator cables to or from the pattern generator module or probe while the logic analyzer is powered on. The recommended DUT (Device Under Test) and pattern generator power on/off sequence is as follows:

Power on the DUT first, then power on the pattern generator. Power off the pattern generator and then power off the DUT.

Although the pattern generator probe cable appears to be a SCSI cable, it is not compatible with a SCSI cable; do not use a SCSI cable with the pattern generator module, or use the pattern generator probe cable with a SCSI instrument.

The probe is fragile; handle it carefully.

### **Connecting the P6475 Probe**

#### P6475 Connections

Do the following steps to connect the P6475 to the logic analyzer, the target system, and to the power source:

- 1. Power off the logic analyzer and the target system before connecting the pattern generator probes.

- **2.** Connect the lead sets to the target system.

- **3.** Connect the P6475 as shown in Figure 2. The probe cable is reversible; either end can be connected to the P6475.

- **4.** Connect the P6475 power cord.

- **5.** Connect the probe to the pattern generator module on the logic analyzer.

### Power On/Off

Follow the procedures below to power on and power off the P6475 variable probe:

- **1.** Power on the DUT

- **2.** Power on the P6475

- **3.** Power on the TLA

- **1.** Power off the TLA

- 2. Power off the P6475

- **3.** Power off the DUT

## Reference

This section provides reference information and specifications for the TLA7PG2 probes.

## **Probe Connectors and Signal Names**

# P6470 and P6474 Pin Assignments

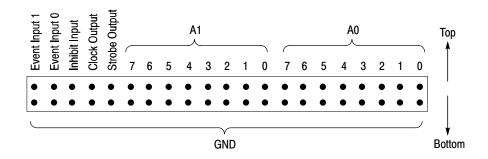

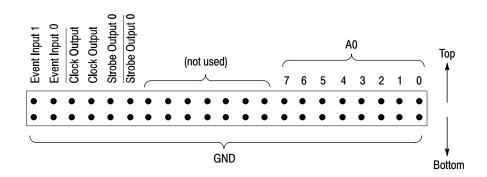

Figure 3 shows the P6470 TTL/CMOS and P6474 LVCMOS pin assignments on the front panel.

Figure 3: P6470 and P6474 output connector pin assignments

#### **P6471 Pin Assignments**

Figure 4 shows the P6471 ECL pin assignments on the front panel.

Figure 4: P6471 output connector pin assignments

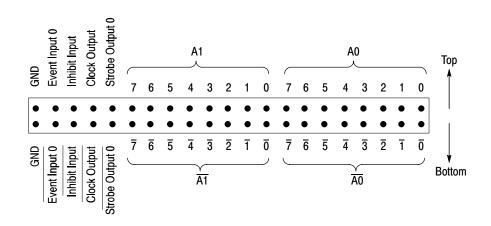

#### **P6472 Pin Assignments**

Figure 5 shows the P6472 PECL/LVPECL pin assignments on the front panel.

Figure 5: P6472 output connector pin assignments

#### **P6473 Pin Assignments**

Figure 6 shows the P6473 LVDS pin assignments on the front panel.

Figure 6: P6473 output connector pin assignments

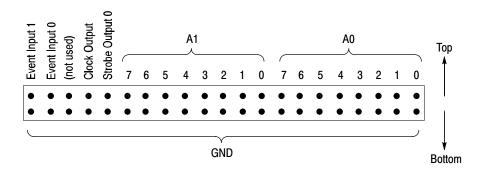

**P6475 Pin Assignments**

Figure 7 shows the P6475 variable pin assignments on the front panel.

Figure 7: P6475 output connector pin assignments

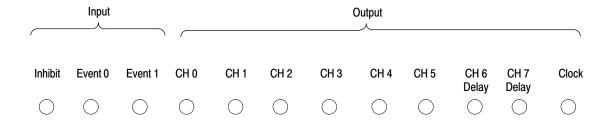

### **Probe Overview**

Table 1 shows the signal names when used with different probes. These signal names appear on the probe labels.

You can have up to four probes connected to each PG module. The leftmost probe will be the master, and the probes to the right of the master are the slaves. The probes are named Probe A, Probe B, Probe C, and Probe D, respectively. Refer to Table 1 for input and output names for each probe.

Table 1: Inputs and outputs of pattern generator probes

| Characteristic             | P6470 TTL/<br>CMOS | P6471 ECL        | P6472 PECL/<br>LVPECL | P6473 LVDS       | P6474 LVCMOS     | P6475 Variable   |

|----------------------------|--------------------|------------------|-----------------------|------------------|------------------|------------------|

| Data Output<br>(Full/Half) | 16/8 channels      | 16/8 channels    | 8/8 channels          | 16/8 channels    | 16/8 channels    | 8/8 channels     |

| Probe A                    | A0 (0 through 7)   | A0 (0 through 7) | A0 (0 through 7)      | A0 (0 through 7) | A0 (0 through 7) | A0 (0 through 7) |

|                            | A1 (0 through 7)   | A1 (0 through 7) |                       | A0 (0 through 7) | A1 (0 through 7) |                  |

|                            |                    |                  |                       | A1 (0 through 7) |                  |                  |

|                            |                    |                  |                       | A1 (0 through 7) |                  |                  |

| Probe B                    | B0 (0 through 7)   | B0 (0 through 7) | B0 (0 through 7)      | B0 (0 through 7) | B0 (0 through 7) | B0 (0 through 7) |

|                            | B1 (0 through 7)   | B1 (0 through 7) |                       | B0 (0 through 7) | B1 (0 through 7) |                  |

|                            |                    |                  |                       | B1 (0 through 7) |                  |                  |

|                            |                    |                  |                       | B1 (0 through 7) |                  |                  |

| Probe C                    | C0 (0 through 7)   | C0 (0 through 7) | C0 (0 through 7)      | C0 (0 through 7) | C0 (0 through 7) | C0 (0 through 7) |

|                            | C1 (0 through 7)   | C1 (0 through 7) |                       | C0 (0 through 7) | C1 (0 through 7) |                  |

|                            |                    |                  |                       | C1 (0 through 7) |                  |                  |

|                            |                    |                  |                       | C1 (0 through 7) |                  |                  |

| Probe D                    | D0 (0 through 7)   | D0 (0 through 7) | D0 (0 through 7)      | D0 (0 through 7) | D0 (0 through 7) | D0 (0 through 7) |

|                            | D1 (0 through 7)   | D1 (0 through 7) |                       | D0 (0 through 7) | D1 (0 through 7) |                  |

|                            |                    |                  |                       | D1 (0 through 7) |                  |                  |

|                            |                    |                  |                       | D1 (0 through 7) |                  |                  |

| Clock Output               | 11                 | 11               | 11                    | 11               | 11               | 1                |

| Probe A                    | CLK                | CLK              | CLK, CLK              | CLK/CLK          | CLK              | CLK              |

| Probe B                    | CLK                | CLK              | CLK, CLK              | CLK/CLK          | CLK              | CLK              |

| Probe C                    | CLK                | CLK              | CLK, CLK              | CLK/CLK          | CLK              | CLK              |

| Probe D                    | CLK                | CLK              | CLK, CLK              | CLK/CLK          | CLK              | CLK              |

Table 1: Inputs and outputs of pattern generator probes (Cont.)

| Characteristic           | P6470 TTL/<br>CMOS | P6471 ECL    | P6472 PECL/<br>LVPECL | P6473 LVDS  | P6474 LVCMOS | P6475 Variable |

|--------------------------|--------------------|--------------|-----------------------|-------------|--------------|----------------|

| Strobe Output            | 1                  | 1            | 1                     | 1           | 1            | 02             |

| Probe A                  | STRB0              | STRB0        | STRB0, STRB0          | STRB0/STRB0 | STRB0        |                |

| Probe B                  | STRB1              | STRB1        | STRB1, STRB1          | STRB2/STRB2 | STRB1        |                |

| Probe C                  | STRB2              | STRB2        | STRB2, STRB2          | STRB4/STRB4 | STRB2        |                |

| Probe D                  | STRB3              | STRB3        | STRB3, STRB3          | STRB6/STRB6 | STRB3        |                |

| Inhibit Input            | 1                  | 0            | 0                     | 1           | 1            | 1              |

| Probe A                  | INHB               |              |                       | INHB/INHB   | INHB         | INHB           |

| Probe B                  | INHB               |              |                       | INHB/INHB   | INHB         | INHB           |

| Probe C                  | INHB               |              |                       | INHB/INHB   | INHB         | INHB           |

| Probe D                  | INHB               |              |                       | INHB/INHB   | INHB         | INHB           |

| Event Input <sup>3</sup> | 2                  | 2            | 2                     | 1           | 2            | 2              |

| Probe A                  | EVNT0, EVNT1       | EVNT0, EVNT1 | EVNT0, EVNT1          | EVNT0/EVNT0 | EVNT0, EVNT1 | EVNT0, EVNT1   |

| Probe B                  | EVNT2, EVNT3       | EVNT2, EVNT3 | EVNT2, EVNT3          | EVNT2/EVNT2 | EVNT2, EVNT3 | EVNT2, EVNT3   |

| Probe C                  | EVNT4, EVNT5       | EVNT4, EVNT5 | EVNT4, EVNT5          | EVNT4/EVNT4 | EVNT4, EVNT5 | EVNT4, EVNT5   |

| Probe D                  | EVNT6, EVNT7       | EVNT6, EVNT7 | EVNT6, EVNT7          | EVNT6/EVNT6 | EVNT6, EVNT7 | EVNT6, EVNT7   |

The Clock Output is disabled when Strobe Output is enabled.

Descriptions of the probe input and output control signals follow. For more information on using the probe signals, refer to the online help for the pattern generator.

**Clock Output.** Each probe has one clock output signal. The logic level of the clock output is the same as the data output.

The clock output is disabled when the strobe output is enabled.

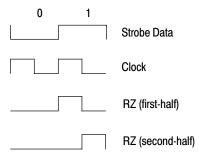

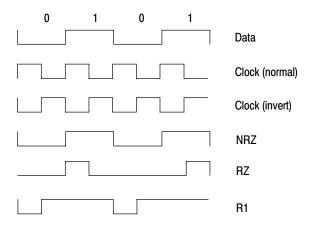

**Strobe Output.** Each probe has a strobe output signal except for the P6475 variable probe. CH 6and CH7 can be used as a strobe signal by setting the data format to RZ/R1.

The logic level of the strobe output is the same as the data output.

The output format of the strobe is RZ (return to zero). The pulse width is the same as the first or the second half of the clock cycle. The pulse can be

<sup>&</sup>lt;sup>2</sup> CH6 and CH7 can be used as Strobe Outputs by setting the data format to RZ/R1.

The External Event Input is used to suspend/resume the sequencer (Advance function) or to jump to a specified line in the sequence or inhibit the output.

positioned at either first half (Strobe delay: Zero) or second half (Strobe delay: Trailing Edge) of the clock cycle.

Figure 8 shows the pulse pattern of the strobe output.

Figure 8: Strobe output pulse pattern

**P6475 Variable probe Output Format.** Figure 9 shows the P6475 output pulse patterns for various signals. NRZ is the output format for CH0 through CH5. You can select NRZ, RZ, and R1 from CH6 and CH7. The delay pulse width using RZ or R1 is equal to half of the clock cycle when using the internal clock mode. The clock output polarity is selectable from Normal or Invert. Refer to the TLA7PG2 for more information.

You can delay the CH6 and CH7 output up to 50 ns. Figure 9 shows the P6475 output pulse pattern.

Figure 9: P6475 Variable probe output pulse pattern

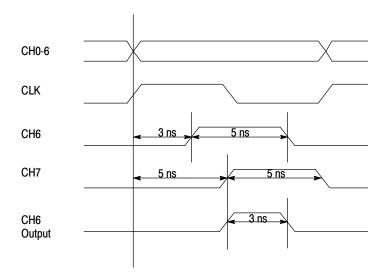

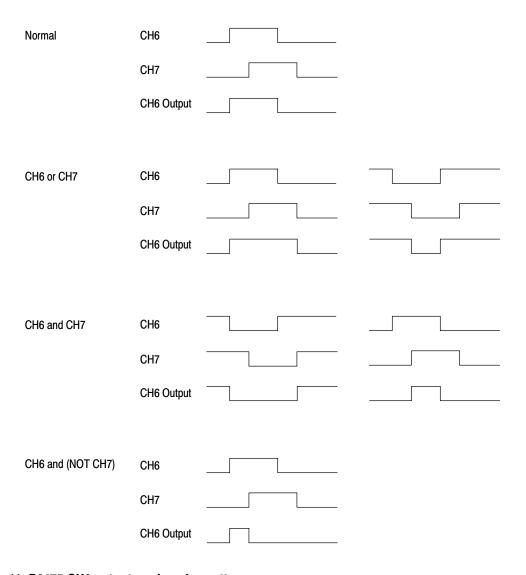

By using the CH6 Output Mode control, it is possible to output a wider or narrower pulse from the CH6 output connector. Figure 11 shows the CH6 and CH7 output pulse patterns when using the CH6 Output Mode control.

For example, if the P6475 is setup as follows:

Clock Frequency: 100 MHz (10 ns period)

CH6: RZ, delay 3 ns

CH7: RZ, delay 5 ns

CH6 Output Mode: CH6 and CH7

The CH6 output will be as shown in Figure 10.

You will see an RZ pulse of 5 ns delay and a 3 ns width at the CH6 output connector

Figure 10: P6475 CH6 output example

Figure 11 shows the various CH6 pulse patterns depending on which mode is setup from the CH6 Output Mode Setup menu. See the TLA7PG2 Online Help system for more information.

Figure 11: P6475 CH6 output mode pulse patterns

**Inhibit Input.** The P6470, P6473, P6474 and P6475 have an inhibit input to set the output to high impedance. The input polarity is positive true and a High input will disable the output. Low input or no connection enables the output. The P6475 input state (High or Low) with no connection will vary according to the input threshold setting.

**External Event Input.** All of the probes have one or two event inputs. The pattern generator detects an event when the external event input is High (True). The external event input is Low (False) when no signal is detected or when the probe

is not connected to the pattern generator. The P6475 input state (High or Low) with no connection will vary according to the input threshold setting.

The external event can be used to Jump or Advance the sequencer or disable the output. The input polarity is positive true.

**Input Logic Level.** All inputs are the same logic level as the output except for the P6475 Variable probe. The  $V_{cc}$  of the input circuit is the same as the  $V_{cc}$  of the output driver for the P6470 TTL/CMOS probe and the P6474 LVCMOS probe. The P6475 Variable probe input threshold level is adjustable within the range of -2.5~V to +2.5~V.

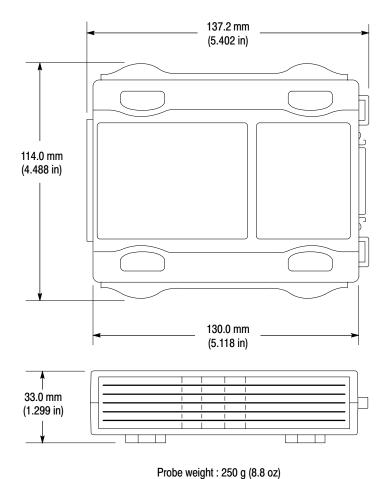

### **Probe Dimensions**

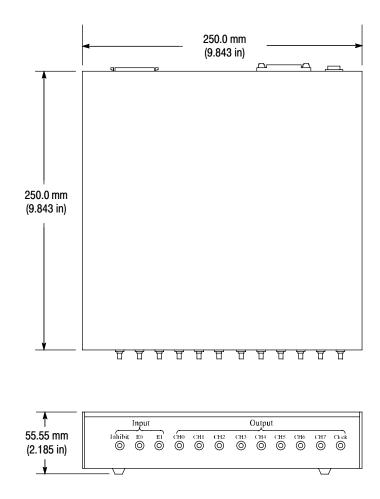

Figure 12 shows the dimensions of the standard pattern generator probes. The physical dimensions are the same for the P6470, P6471, P6472, P6473, and P6474 probes.

**NOTE**. There are no ventilation requirements for the standard probes.

Figure 12: P6470, P6471, P6472, P6473 and P6474 probe dimensions

Figure 13 shows the dimensions of the P6475 probe.

Figure 13: P6475 Variable probe dimensions

## **P6475 Installation Requirements**

Table 2 provides information for the P6475 Variable probe installation:

Table 2: P6475 Variable probe installation requirements

| Characteristics           | Description                                                                                    |  |  |

|---------------------------|------------------------------------------------------------------------------------------------|--|--|

| Maximum power dissipation | 35 W max. Maximum line current is 0.6 $\ensuremath{A_{rms}}$ at 50 Hz,                         |  |  |

| (fully loaded)            | 90 V line, with 5 % clipping                                                                   |  |  |

| Surge Current             | Max 57 A peak (25° C) $\leq$ 5 line cycles after product has been turned off for at least 30 s |  |  |

| Clearance for ventilation |                                                                                                |  |  |

| Side                      | 10 cm (3.9 in)                                                                                 |  |  |

## **Input/Output Circuits**

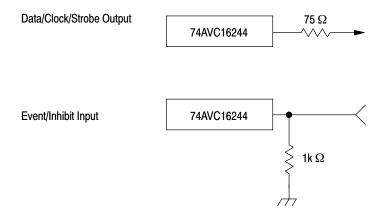

This subsection shows the input/output circuits for the P6470, P6471, P6472, P6473. and P6474 probes.

#### P6470

Figure 14 shows the probe input/output circuit for the P6470 TTL/CMOS pattern generator probe. The P6470 comes standard with 75  $\Omega$  resistor packs. You can change the resistor packs to provide impedance matching for the target system.

The P6470 provides 16 data outputs, 1 clock output, and 1 strobe output.

Figure 14: P6470 input/output circuit

**P6471** Figure 15 shows the probe input/output circuit for the P6471 ECL pattern generator probe.

The P6471 provides 16 data outputs, 1 clock output, and 1 strobe output.

Figure 15: P6471 input/output circuit

**P6472** Figure 16 shows the input/output circuit for the P6472 PECL/LVPECL pattern generator probe. The P6472 provides PECL/LVPECL signals to the target system and contains 8 data outputs, 1 clock output, and 1 strobe output.

Figure 16: P6472 input/output circuit

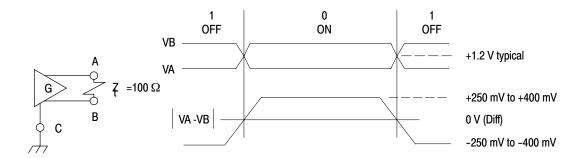

**P6473** The P6473 LVDS is compatible with the TIA/EIA-644 standard.

A generator circuit in the probe produces a balanced source that results in a differential voltage across a test termination load of  $100\,\Omega$  in the range of 250 mV to 450 mV.

Figure 17 illustrates the signaling sense of the voltages appearing across the termination resistor.

- The A terminal of the generator is negative with respect to the B terminal for a binary 1 or OFF state.

- The A terminal of the generator is positive with respect to the B terminal for a binary 0 or ON state.

Figure 17: Signaling sense

#### P6474

Figure 18 shows the input/output circuit for the P6474 LVCMOS pattern generator probe. The P6474 provides LVCMOS signals to the target system and contains 16 data outputs, one clock output and one strobe output. You can adjust the  $V_{cc}$  of the output driver and the input receiver from 1.2 V to 3.3 V. The P6474 comes standard with 75  $\Omega$  resistor packs. You can change the resistor packs to provide impedance matching for the target system.

The P6474 provides 16 data outputs, 1 clock output and 1 strobe output.

Figure 18: P6474 input/output circuit

## **Timing Diagrams**

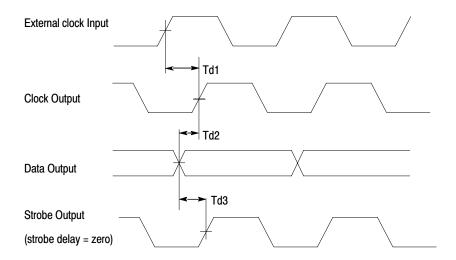

Figures 19 through 24 show the pattern generator timing diagrams. The diagrams apply to all probes unless otherwise stated.

Figure 19: Clock and strobe timing diagram

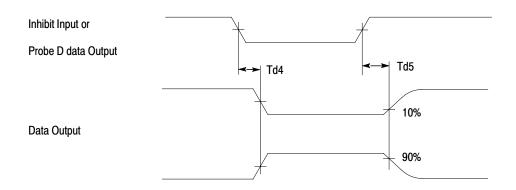

Figure 20: P6470, P6472, P6473, and P6474 inhibit timing diagram

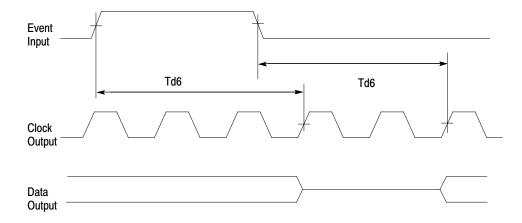

Figure 21: P6470, P6472, P6473, and P6474 external event for inhibit timing diagram

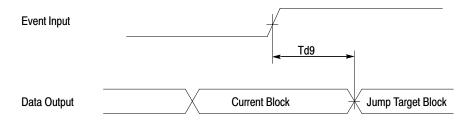

Figure 22: External event for jump timing diagram

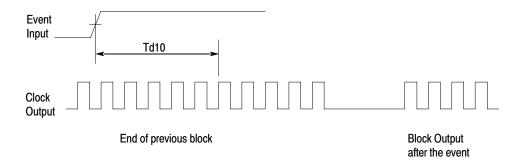

Figure 23: External event for half channel advance timing diagram

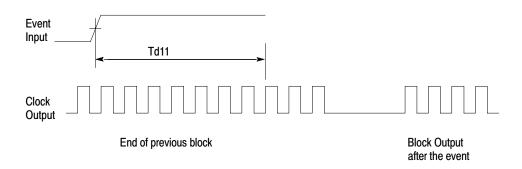

Figure 24: External event for full channel advance timing diagram

Figure 25: External event for delay to data output for advance diagram

# **Specifications**

The specifications apply to all versions of the pattern generator unless otherwise noted.

#### Table 3: P6470 TTL/CMOS probe

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +5 V Series Termination Resistor: 75  $\Omega$

Load: 510  $\Omega$  + 50 pF

| Characteristic                                                                                                                 | Description                                                                                |                      |                   |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------|-------------------|

| Maximum Clock Frequency (with series termination resistor: 75 $\Omega$ )                                                       | Output Level (V <sub>cc</sub> )                                                            | Full Channel mode    | Half Channel mode |

|                                                                                                                                | Vcc ≤ 3.3 V                                                                                | 134 MHz              | 268 MHz           |

|                                                                                                                                | 3.3 V < Vcc ≤ 5 V                                                                          | 62.5 MHz             | 125 MHz           |

|                                                                                                                                | Vcc > 5 V                                                                                  | 52.5 MHz             | 105 MHz           |

| Maximum Clock Frequency (with series termination resistor: 75 $\Omega$ , load: 10 k $\Omega$ + 15 pf, sample output pattern: 8 | Output Level (V <sub>cc</sub> )                                                            | Full Channel mode    | Half Channel mode |

| bit counter)  Typical                                                                                                          | Vcc ≤ 5.5 V                                                                                | 134 MHz              | 268 MHz           |

| Output Level (V <sub>CC</sub> )                                                                                                | 2.0 V to 5.5 V, 25 mV ste                                                                  | p, into 1 M $\Omega$ |                   |

| Maximum Resistive Load                                                                                                         | 220 Ω                                                                                      |                      |                   |

| Maximum Capacitive Load                                                                                                        | 50 pF                                                                                      |                      |                   |

| Output Type                                                                                                                    | 74LVC541A for Data Output<br>74LVC244A for Clock/Strobe Output                             |                      |                   |

| Series Termination Resistor                                                                                                    | 75 $\Omega$ standard. 43, 100 and 150 $\Omega$ as optional accessories (18 pin DIP socket) |                      |                   |

| Supported Channel Mode                                                                                                         | Half and Full                                                                              |                      |                   |

| Number of External Inhibit Inputs                                                                                              | 1                                                                                          |                      |                   |

| Rise/Fall Time (20% to 80% load: 1 M $\Omega$ +< 1 pF) Typical                                                                 | Clock/Strobe Output Rise 640 ps Fall 1.1 ns Data Output Rise 680 ps Fall 2.9 ns            |                      |                   |

| Rise/Fall Time (20% to 80% load: 510 $\Omega$ + 51 pF)<br>Typical                                                              | Clock/Strobe Output Rise 6.5 ns Fall 6.3 ns Data Output Rise 5.2 ns Fall 4.5 ns            |                      |                   |

## Table 3: P6470 TTL/CMOS probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +5 V Series Termination Resistor: 75  $\Omega$

Load: 510  $\Omega$  + 50 pF

| Characteristic                                                                                | Description                                                                                                                                                         |  |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Output Skew<br>Typical                                                                   | < 570 ps between all data output pins of all modules in the mainframe after intermodule skew is adjusted manually                                                   |  |

|                                                                                               | < 480 ps between all data output pins of all probes of single module                                                                                                |  |

|                                                                                               | < 440 ps between all data output pins of single probe                                                                                                               |  |

| Data Output to Strobe Output Delay<br>Typical                                                 | + 1.7 ns when strobe delay set to zero. (Td3 in Figure 19 on page 22)                                                                                               |  |

| Data Output to Clock Output Delay<br>Typical                                                  | +2.4 ns (Td2 in Figure 19 on page 22)                                                                                                                               |  |

| External Clock Input to Clock Output Delay<br>Typical                                         | 61 ns (Td1 in Figure 19 on page 22)                                                                                                                                 |  |

| External Inhibit Input to Output Enable Delay Typical                                         | 34 ns for Data Output (Td4 in Figure 20 on page 23)                                                                                                                 |  |

| External Inhibit Input to Output Disable Delay <i>Typical</i>                                 | 86 ns for Data Output (Td5 in Figure 20 on page 23)                                                                                                                 |  |

| Probe D Data Output to Output Enable Delay (for Internal Inhibit) <i>Typical</i>              | 7 ns for Data Output (Td4 in Figure 20 on page 23)                                                                                                                  |  |

| Probe D Data Output to Output Disable Delay (for Internal Inhibit) <i>Typical</i>             | 8 ns for Data Output (Td5 in Figure 20 on page 23)                                                                                                                  |  |

| External Event Input to Clock Output Setup                                                    | Full channel mode: 1.5 clocks + 240 ns (Td6 in Figure 21 on page 23)                                                                                                |  |

| (for inhibit)<br>(event-filter: off) <i>Typical</i>                                           | Half channel mode: 2 clocks + 240 ns                                                                                                                                |  |

| External Event Input and Inhibit Input<br>Input Type<br>Minimum Pulse Width                   | 74LVC14A, Positive True, 1 kΩ to GND 200 ns (event filter: off)                                                                                                     |  |

| External Event Input Delay to Data Output for                                                 | 230 ns to 330 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 25 on page 24)                                                                                                   |  |

| Advance                                                                                       | (CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock period when the External Clock is used.)                                      |  |

| External Event Input Number of Inputs Setup Time of Event <i>Typical</i> Input for Event Jump | 2 Half Channel Mode 54 to 61 clocks + 240 ns before the next block Full Channel Mode 27.5 to 31 clocks + 240 ns before the next block (Td9 in Figure 22 on page 23) |  |

# Table 3: P6470 TTL/CMOS probe (Cont.)

All timing values are specified at the probe connector under the conditions listed below, unless otherwise noted:

Output Voltage setting: +5 V Series Termination Resistor: 75  $\Omega$

Load: 510  $\Omega$  + 50 pF

| Characteristic                                                                                                                   | Description                                                                                                                                                                                                                                                                                     |  |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Setup Time of Event Input for Event Advance<br>Typical                                                                           | In Half Channel Mode, 240 ns before the rising edge of 5th clock output pulse from the last of the previous block (Td10 in Figure 23 on page 24) In Full Channel Mode, 240 ns before the rising edge of 3rd clock output pulse from t last of the previous block (Td11 in Figure 24 on page 24) |  |

| Mainframe External Signal Input to PG Probe data output for Advance via Signal 1, 2 Typical via Signal 3, 4 Typical              | 200 ns to 300 ns + 1.5 to 2.5 CLK2 230 ns to 330 ns + 1.5 to 2.5 CLK2 (CLK2 is from 2.5 ns to 5 ns when the Internal Clock is used. It is the same as one clock period when the External Clock is used)                                                                                         |  |

| for Inhibit<br>via Signal 1, 2 <i>Typical</i>                                                                                    | 100 ns to 200 ns + 2 to 3 CLK (Half Channel Mode) 100 ns to 200 ns + 1.5 to 2.5 CLK (Full Channel Mode)                                                                                                                                                                                         |  |

| via Signal 3, 4 <i>Typical</i>                                                                                                   | 130 ns to 230 ns+ 2 to 3 CLK (Half Channel Mode) 130 ns to 230 ns + 1.5 to 2.5 CLK (Full Channel Mode)                                                                                                                                                                                          |  |

| PG Probe Clock Output to Mainframe External<br>Signal Output<br>via Signal 1, 2 <i>Typical</i><br>via Signal 3, 4 <i>Typical</i> | 18 ns - 5 CLK (Half Channel Mode) 18 ns - 3 CLK (Full Channel Mode) 29 ns - 5 CLK (Half Channel Mode) 29 ns - 3 CLK (Full Channel Mode)                                                                                                                                                         |  |

| Number of Data Outputs                                                                                                           | 16 in Full Channel Mode<br>8 in Half Channel Mode                                                                                                                                                                                                                                               |  |

| Number of Clock Outputs                                                                                                          | 1                                                                                                                                                                                                                                                                                               |  |

| Number of Strobe Outputs                                                                                                         | 1 (Only one Clock Output or Strobe Output can be enabled at one time per probe)                                                                                                                                                                                                                 |  |

| Number of External Event Inputs                                                                                                  | 2                                                                                                                                                                                                                                                                                               |  |

| Clock Output Polarity                                                                                                            | Positive                                                                                                                                                                                                                                                                                        |  |

| Strobe Type                                                                                                                      | RZ only                                                                                                                                                                                                                                                                                         |  |

Table 4: P6471 ECL probe

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted: Load: 51  $\Omega$  terminated to -2 V

| Characteristic                                                                         | Description                                                                                                                                                                                       |  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Maximum Clock Frequency                                                                | 134 MHz in Full Channel mode<br>268 MHz in Half Channel mode                                                                                                                                      |  |

| Output Level                                                                           | ECL                                                                                                                                                                                               |  |

| Output Type                                                                            | 100E151 for data output 100EL16 for strobe output 100EL04 for clock output outputs are unterminated                                                                                               |  |

| Supported Channel Mode                                                                 | Half and Full                                                                                                                                                                                     |  |

| Rise/Fall Time<br>(20% to 80%) <i>Typical</i>                                          | Clock Output Rise 320 ps Fall 330 ps Data Output Rise 1,200 ps Fall 710 ps Strobe Output Rise 290 ps Fall 270 ps                                                                                  |  |

| Data Output Skew Typical                                                               | < 255 ps between all data output pins of all modules in the mainframe after intermodule skew is adjusted manually < 240 ps between all data output pins of all probes of single module            |  |

| Data Output to Strobe Output Delay<br>Typical                                          | < 210 ps between all data output pins of a single probe<br>+2.94 ns when strobe delay set to zero (Td3 in Figure 19 on page 22)                                                                   |  |

| Data Output to Clock Output Delay<br>Typical                                           | +780 ps (Td2 in Figure 19 on page 22)                                                                                                                                                             |  |

| External Clock Input to Clock Output Delay<br>Typical                                  | 50 ns (Td1 in Figure 19 on page 22)                                                                                                                                                               |  |

| External Event Input Delay to Data Output for Advance                                  | 170 ns to 270 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 25 on page 24)  (CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock period when the External Clock is used.) |  |

| External Event Input<br>Input Level<br>Input Type<br>Minimum Pulse Width               | ECL 10H116 with 75 k $\Omega$ to -2 V 150 ns (Event filter: off)                                                                                                                                  |  |

| External Event Input Number of Inputs Setup Time of Event Input for Event Jump Typical | 2 Half Channel Mode, 54 to 61 clocks + 180 ns before the next block Full Channel Mode, 27.5 to 31 clocks + 180 ns before the next block (Td9 in Figure 22 on page 23)                             |  |

## Table 4: P6471 ECL probe (Cont.)

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted: Load: 51  $\Omega$  terminated to -2 V

| Characteristic                                                                                                                                | Description                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Setup Time of Event<br>Input for Event Advance<br>Typical                                                                                     | Half Channel Mode:<br>80 ns before the rising edge of 5th clock output pulse from the last of the<br>previous block (Td10 in Figure 23 on page 24)                                        |

|                                                                                                                                               | Full Channel Mode<br>80 ns before the rising edge of 3rd clock output pulse from the last of the<br>previous block (Td11 in Figure 24 on page 24)                                         |

| Mainframe External Signal Input to PG Probe<br>data output<br>for Advance<br>via Signal 1, 2 <i>Typical</i><br>via Signal 3, 4 <i>Typical</i> | 200 ns to 300 ns + 1.5 to 2.5 CLK2 230 ns to 330 ns + 1.5 to 2.5 CLK2 (CLK2 from 2.5 ns to 5 ns when Internal Clock is used. It is same as one clock period when External Clock is used.) |

| PG Probe Clock Output to Mainframe External<br>Signal Output<br>via Signal 1, 2 <i>Typical</i><br>via Signal 3, 4 <i>Typical</i>              | 28 ns - 5 CLK (Half Channel Mode) 28 ns - 3 CLK (Full Channel Mode) 38 ns - 5 CLK (Half Channel Mode) 38 ns - 3 CLK (Full Channel Mode)                                                   |

| Number of Data Outputs                                                                                                                        | 16 in Full Channel Mode<br>8 in Half Channel Mode                                                                                                                                         |

| Number of Clock Outputs                                                                                                                       | 1                                                                                                                                                                                         |

| Number of Strobe Outputs                                                                                                                      | 1 (Only one Clock Output or one Strobe Output can be enabled at one time per probe)                                                                                                       |

| Number of External Event Inputs                                                                                                               | 2                                                                                                                                                                                         |

| Clock Output Polarity                                                                                                                         | Positive                                                                                                                                                                                  |

| Strobe Type                                                                                                                                   | RZ only                                                                                                                                                                                   |

Table 5: P6472 PECL/LVPECL probe

All timing values are specified with a load condition of 1 M  $\Omega$  +  $\leq$  1 pF with PECL mode.

| Characteristic                                | Description                                                                                                                    |                                           |  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

| Maximum Clock Frequency                       | Full Channel Mode                                                                                                              | Half Channel Mode                         |  |

|                                               | 134 MHz                                                                                                                        | 268 MHz                                   |  |

| Number of Data Outputs                        | 8 Full Channel                                                                                                                 |                                           |  |

|                                               | 8 Half Channel                                                                                                                 |                                           |  |

| Number of Clock Outputs                       | 1 differential                                                                                                                 |                                           |  |

| Number of Strobe Outputs                      | 1 differential                                                                                                                 |                                           |  |

|                                               | (Only one Clock Output or one Strobe Out                                                                                       | put can be enabled at one time per probe) |  |

| Number of External Event Inputs               | 2                                                                                                                              |                                           |  |

| Clock Output Polarity                         | Positive                                                                                                                       |                                           |  |

| Strobe Type                                   | RZ (return to zero) only                                                                                                       |                                           |  |

| Strobe Delay                                  | Zero or Trailing Edge                                                                                                          |                                           |  |

| Output Level                                  | PECL, LVPECL (selectable by moving a ju                                                                                        | imper in the probe)                       |  |

| Output Type                                   | 100EL90 (all outputs are terminated)                                                                                           |                                           |  |

| Supported Channel Mode                        | Half and Full                                                                                                                  |                                           |  |

| Rise/Fall Time (20% to 80%)                   | Rise 430 ps                                                                                                                    |                                           |  |

|                                               | Fall 970 ps                                                                                                                    |                                           |  |

| Data Output Skew                              | < 385 ps between all data output pins of a intermodule skew is adjusted manually                                               | Il modules in the mainframe after         |  |

|                                               | < 370 ps between all data output pins of all probes of single module                                                           |                                           |  |

|                                               | < 340 ps between all data output pins of a single probe                                                                        |                                           |  |

| Data Output to Strobe Output Delay            | + 2.93 ns when strobe delay is set to zero (See Td3 in Figure 19 on page 22)                                                   |                                           |  |

| Data Output to Clock Output Delay             | + 1.12 ns (Td2 in Figure 19 on page 22)                                                                                        |                                           |  |

| External Clock Input to Clock Output Delay    | 50 ns (See Td1 in Figure 19 on page 22)                                                                                        |                                           |  |

| External Event Input Delay to Data Output for | 170 ns to 270 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 25 on page 24)                                                              |                                           |  |

| Advance                                       | (CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock period when the External Clock is used.) |                                           |  |

| External Event Input                          |                                                                                                                                |                                           |  |

| Input Level                                   | PECL, LVPECL (selectable by moving a jumper in the probe)                                                                      |                                           |  |

| Input Type                                    | 100EL91, unterminated                                                                                                          |                                           |  |

| Minimum Pulse Width (event filter: off)       | 150 ns                                                                                                                         |                                           |  |

## Table 5: P6472 PECL/LVPECL probe (Cont.)

All timing values are specified with a load condition of 1 M  $\Omega$  +  $\leq$  1 pF with PECL mode.

| Characteristic                                            | Description                                                                                                                                           |  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| External Event Input                                      |                                                                                                                                                       |  |

| Setup Time of Event Input for Event Jump                  | Half Channel Mode: 54 to 61 Clocks + 180 ns before the next block Full Channel Mode: 27.5 to 31 Clocks + 180 ns before the next block                 |  |

|                                                           | (see Td9 in Figure 22 on page 23)                                                                                                                     |  |

| Setup Time of Event Input for Event Advance               | Half Channel Mode: 180 ns before the rising edge of the 5th clock output pulse from the last of the previous block (See Td10 in Figure 23 on page 24) |  |

|                                                           | Full Channel Mode: 180 ns before the rising edge of the 3rd clock output pulse from the last of the previous block (see Td11 in Figure 24 on page 24) |  |

| Mainframe External Signal Input to PG Probe Data Output   |                                                                                                                                                       |  |

| For Advance:                                              |                                                                                                                                                       |  |

| Using signal 1 or 2                                       | 200 ns to 300 ns + 1.5 to 2.5 CLK2                                                                                                                    |  |

| Using signal 3 or 4                                       | 230 ns to 330 ns + 1.5 to 2.5 CLK2                                                                                                                    |  |

|                                                           | (CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock period when the External Clock is used.)                        |  |

| PG Probe Clock Output to Mainframe External Signal Output |                                                                                                                                                       |  |

| Using signal 1 or 2                                       | 31 ns -5 CLK (Half Channel Mode)                                                                                                                      |  |

| Union signal O or 4                                       | 31 ns -3 CLK (Full Channel Mode)                                                                                                                      |  |

| Using signal 3 or 4                                       | 40 ns -5 CLK (Half Channel Mode)                                                                                                                      |  |

|                                                           | 40 ns -3 CLK (Full Channel Mode)                                                                                                                      |  |

# Table 6: P6473 LVDS probe

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted: Load: 100  $\Omega$  + < 1 pF

| Characteristic          | Description       | Description       |  |

|-------------------------|-------------------|-------------------|--|

| Maximum Clock Frequency | Full Channel Mode | Half Channel Mode |  |

|                         | 134 MHz           | 268 MHz           |  |

| Number of Data Outputs  | 16 Full Channel   |                   |  |

|                         | 8 Half Channel    |                   |  |

# Table 6: P6473 LVDS probe (Cont.)

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted: Load: 100  $\Omega$  + < 1 pF

| Characteristic                                 | Description                                                                                                                    |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Number of Clock Outputs                        | 1 (Only one Clock Output or One Strobe Output can be enabled at one time per probe.)                                           |  |

| Number of Strobe Outputs                       | 1 (Only one Clock Output or One Strobe Output can be enabled at one time per probe.)                                           |  |

| Number of External Event Inputs                | 1                                                                                                                              |  |

| Number of External Inhibit Inputs              | 1                                                                                                                              |  |

| Clock Output Polarity                          | Positive                                                                                                                       |  |

| Strobe Type                                    | RZ (return to zero) only                                                                                                       |  |

| Strobe Delay                                   | Zero or Trailing Edge                                                                                                          |  |

| Maximum Capacitive Load                        | 10 pF                                                                                                                          |  |

| Output Type                                    | LVDS (TIA/EIA-644 compatible)                                                                                                  |  |

| Supported Channel Mode                         | Half and Full                                                                                                                  |  |

| Rise/Fall Time                                 | Rise: 910 ps                                                                                                                   |  |

| (20% to 80%)                                   | Fall: 750 ps                                                                                                                   |  |

| Data Output Skew                               | < 365 ps between all data output pins of all modules in the mainframe after intermodule skew is adjusted manually              |  |

|                                                | < 350 ps between all data output pins of all probes of single module                                                           |  |

|                                                | < 320 ps between all data output pins of a single probe                                                                        |  |

| Data Output to Strobe Output Delay             | -280 ns when strobe delay is set to zero (See Td3 in Figure 19 on page 22)                                                     |  |

| Data Output to Clock Output Delay              | 1.2 ns (Td2 in Figure 19 on page 22)                                                                                           |  |

| External Clock Input to Clock Output Delay     | 55 ns (See Td1 in Figure 19 on page 22 )                                                                                       |  |

| External Inhibit Input to Output Enable Delay  | 9 ns for Data Output (See Td4 in Figure 20 on page 23)                                                                         |  |

| External Inhibit Input to Output Disable Delay | 12 ns for Data Output (See Td5 in Figure 20 on page 23)                                                                        |  |

| Probe D Data Output to Output Enable Delay     | 2 ns for Data Output (See Td4 in Figure 20 on page 23)                                                                         |  |

| (for Internal Inhibit)                         |                                                                                                                                |  |

| Probe D Data Output to Output Disable Delay    | 5 ns for Data Output (See Td5 in Figure 20 on page 23)                                                                         |  |

| (for Internal Inhibit)                         |                                                                                                                                |  |

| External Event Input to Clock Output Setup     | Full Channel mode: 1.5 Clocks + 180 ns                                                                                         |  |

| (for inhibit) event-filter: off                | Half Channel mode: 2 Clocks + 180 ns                                                                                           |  |

|                                                | (See Td6 in Figure 21 on page 23)                                                                                              |  |

| External Event Input Delay to Data Output for  | 170 ns to 270 ns + 1.5 to 2.5 CLK2 (Td12 in Figure 25 on page 24)                                                              |  |

| Advance                                        | (CLK2 is from 2.5 ns to 5 ns when Internal Clock is used. It is the same as one clock period when the External Clock is used.) |  |

# Table 6: P6473 LVDS probe (Cont.)

All timing values are specified at the probe connector under the condition listed below, unless otherwise noted: Load: 100  $\Omega$  + < 1 pF